# **Dual Adjustable Voltage Detector** with Reset and Gate Driver Outputs

#### GENERAL DESCRIPTION

The SGM852 is a dual adjustable voltage detector with reset and gate driver outputs. Two adjustable sense inputs can monitor a wide voltage range through external resistor dividers. The device has internal sequence timing. The delay time of two outputs can be programmed by their respective external capacitors. The gate driver output is implemented for external N-MOSFET by a charge pump circuit.

Two options are available. When both VSEN1 and VSEN2 voltages exceed the internal fixed rising threshold voltage in SGM852A, or VSEN1 voltage exceeds the internal fixed rising threshold and VSEN2 voltage falls below the internal fixed falling threshold in SGM852B, both internal comparators output high, the reset output (nRESET) asserts high after a propagation delay and a capacitor charge set-time delay. And if either of the comparators outputs low, nRESET asserts low.

The SGM852 is available in a Green TDFN-3×3-10L package. It operates over a junction temperature range of -40°C to +125°C.

#### **FEATURES**

- Operating Voltage Range: 3V to 16V

- Low Dual Adjustable Threshold:

- Rising Threshold: 0.6V (TYP)

- Falling Threshold: 0.55V (TYP)

- High Threshold Accuracy:

- Rising Threshold Accuracy: ±1.5%

- Falling Threshold Accuracy: ±2%

- Push-Pull Reset Output

- Gate Driver Output

- Capacitor-Adjustable Delay Time

- Available in a Green TDFN-3×3-10L Package

# **APPLICATIONS**

Power Sequencing and Reset Sequencing

Power Switching

Portable Equipment

Computers/Servers

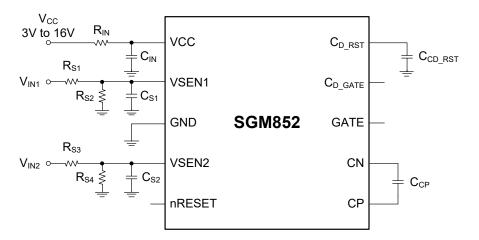

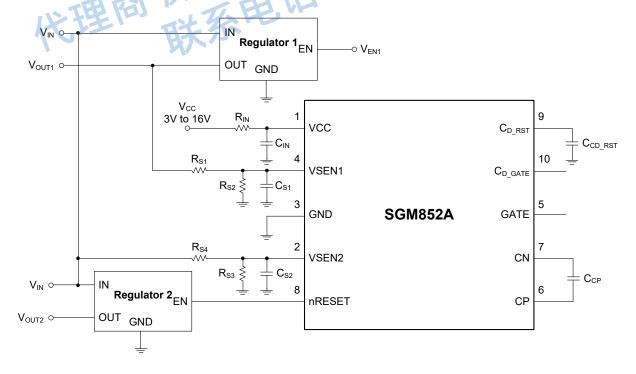

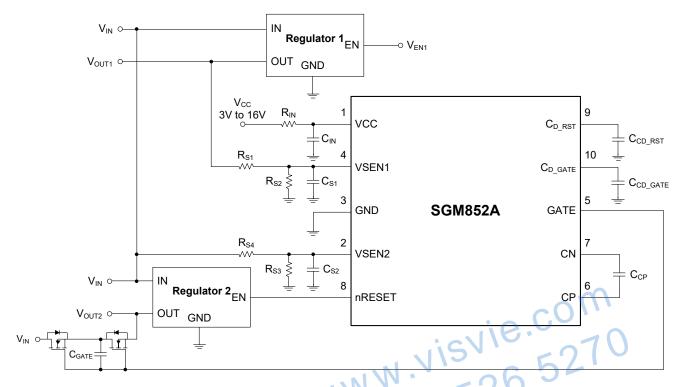

#### TYPICAL APPLICATION

**Figure 1. Typical Application Circuit**

#### PACKAGE/ORDERING INFORMATION

| MODEL   | PACKAGE<br>DESCRIPTION | TEMPERATURE     |                  | PACKAGE<br>MARKING    | PACKING<br>OPTION   |

|---------|------------------------|-----------------|------------------|-----------------------|---------------------|

| SGM852A | TDFN-3×3-10L           | -40°C to +125°C | SGM852AXTD10G/TR | SGM<br>852AD<br>XXXXX | Tape and Reel, 4000 |

| SGM852B | TDFN-3×3-10L           | -40°C to +125°C | SGM852BXTD10G/TR | SGM<br>852BD<br>XXXXX | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| VCC                                                      | 0.3V to 24V   |

|----------------------------------------------------------|---------------|

| VSEN1, VSEN2                                             | 0.3V to 3.5V  |

| CP, GATE                                                 | 0.3V to 12.6V |

| All Other Pins                                           | 0.3V to 6V    |

| Package Thermal Resistance                               | MITTER W      |

| Package Thermal Resistance TDFN-3×3-10L, θ <sub>JA</sub> |               |

| Junction Temperature                                     | +150°C        |

| Storage Temperature Range                                |               |

| Lead Temperature (Soldering, 10s)                        | +260°C        |

| ESD Susceptibility                                       |               |

| HBM                                                      | 3000V         |

| CDM                                                      | 1000V         |

#### RECOMMENDED OPERATING CONDITIONS

| VSEN1, VSEN2                            | 0V to 3V        |

|-----------------------------------------|-----------------|

| Operating Supply Range, V <sub>CC</sub> | 3V to 16V       |

| Operating Junction Temperature Range    | -40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

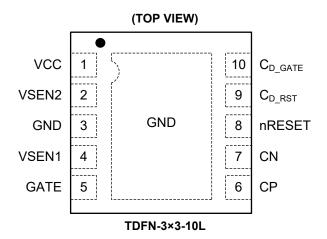

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN | NAME                | FUNCTION                                                                                                                                                                                                                                                       |

|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCC                 | Supply Voltage.                                                                                                                                                                                                                                                |

| 2   | VSEN2               | Input Sense Voltage Pin 2.                                                                                                                                                                                                                                     |

| 3   | GND                 | Ground Pin. GND is connected to the exposed pad and soldered to a large PCB for maximum power dissipation.                                                                                                                                                     |

| 4   | VSEN1               | Input Sense Voltage Pin 1.                                                                                                                                                                                                                                     |

| 5   | GATE                | N-MOSFET Gate Driver Output.                                                                                                                                                                                                                                   |

| 6   | CP                  | Charge Pump Capacitor Pin. Positive Node.                                                                                                                                                                                                                      |

| 7   | CN                  | Charge Pump Capacitor Pin. Negative Node.                                                                                                                                                                                                                      |

| 8   | nRESET              | Active-Low Push-Pull Reset Output Pin. For SGM852A, it goes high when both VSEN1 and VSEN2 exceed the rising threshold voltage. For SGM852B, it goes high when VSEN1 exceeds the rising threshold voltage and VSEN2 falls below the falling threshold voltage. |

| 9   | $C_{D_{RST}}$       | Capacitor to Set Delay Time for nRESET Pin. Connect this pin to GND through an external capacitor to set the reset delay time. Leave this pin open to set faster delay time.                                                                                   |

| 10  | C <sub>D_GATE</sub> | Capacitor to Set Delay Time for Gate Pin. Connect this pin to GND through an external capacitor to set the GATE delay time. Leave this pin open to set faster delay time.                                                                                      |

## **ELECTRICAL CHARACTERISTICS**

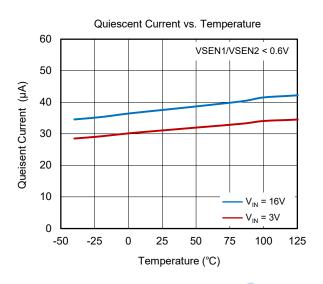

( $V_{CC}$  = 16V,  $T_J$  = -40°C to +125°C, typical values are at  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                 | SYMBOL                   | CONDITIONS                                                                                                                                                                                           | MIN   | TYP                 | MAX   | UNITS |  |  |  |

|-------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------|-------|-------|--|--|--|

| vcc                                       |                          |                                                                                                                                                                                                      |       | •                   |       |       |  |  |  |

| Operating Voltage                         | V <sub>CC</sub>          |                                                                                                                                                                                                      | 3     |                     | 16    | V     |  |  |  |

| Supply Current                            | I <sub>cc</sub>          | Charge pump off                                                                                                                                                                                      |       | 39                  | 66    | μΑ    |  |  |  |

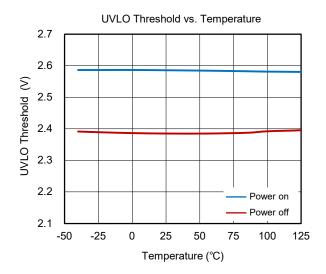

| POR Threshold                             | $V_{POR}$                |                                                                                                                                                                                                      | 2.5   | 2.6                 | 2.7   | V     |  |  |  |

| POR Hysteresis                            | $\Delta V_{PHYS}$        |                                                                                                                                                                                                      |       | 200                 |       | mV    |  |  |  |

| SENSE1/SENSE2                             |                          |                                                                                                                                                                                                      |       |                     |       |       |  |  |  |

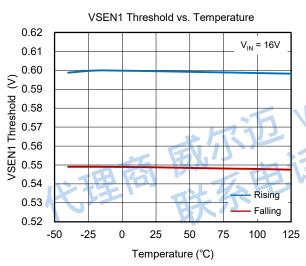

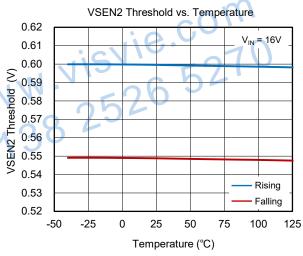

| Rising Threshold                          | $V_{RTH}$                |                                                                                                                                                                                                      | 0.591 | 0.6                 | 0.609 | V     |  |  |  |

| Falling Threshold                         | $V_{FTH}$                |                                                                                                                                                                                                      | 0.539 | 0.55                | 0.561 | V     |  |  |  |

| Hysteresis                                | $\Delta V_{\text{RHYS}}$ |                                                                                                                                                                                                      |       | 50                  |       | mV    |  |  |  |

| Input Current                             | I <sub>SENSE</sub>       | V <sub>SENx</sub> < 1V                                                                                                                                                                               | -100  |                     | 100   | nA    |  |  |  |

| nRESET                                    |                          |                                                                                                                                                                                                      |       |                     |       |       |  |  |  |

|                                           |                          | Logic-High, V <sub>CC</sub> = 3V, I <sub>R</sub> = -2mA                                                                                                                                              | 2.6   | 2.87                | 3     |       |  |  |  |

|                                           | V                        | Logic-High, V <sub>CC</sub> = 4V I <sub>R</sub> = -2mA                                                                                                                                               | 3.6   | 3.88                | 4     |       |  |  |  |

| nRESET Output Voltage                     | V <sub>OH</sub>          | Logic-High, V <sub>CC</sub> = 5V, I <sub>R</sub> = -2mA                                                                                                                                              | 3.9   | 4.68                | 5     | V     |  |  |  |

|                                           |                          | Logic-High, V <sub>CC</sub> > 5.5V, I <sub>R</sub> = -2mA 3.9                                                                                                                                        | 3.9   | 4.54                | 5.5   |       |  |  |  |

|                                           | V <sub>OL</sub>          | Logic-Low, I <sub>R</sub> = 2mA                                                                                                                                                                      | 0     |                     | 0.4   |       |  |  |  |

| Timing                                    |                          | 11/12.                                                                                                                                                                                               |       | 37                  |       |       |  |  |  |

| C <sub>D_RST</sub> Source Current         | I <sub>CD_RST</sub>      | V <sub>SEN1</sub> > 0.6V, V <sub>SEN2</sub> > 0.6V for SGM852A<br>V <sub>SEN1</sub> > 0.6V, V <sub>SEN2</sub> < 0.55V for SGM852B                                                                    | 0.925 | 1                   | 1.075 | μA    |  |  |  |

| C <sub>D_GATE</sub> Source Current        | I <sub>CD_GATE</sub>     | V <sub>SEN1</sub> > 0.6V, V <sub>SEN2</sub> < 0.55V for SGM852B<br>V <sub>SEN1</sub> > 0.6V, V <sub>SEN2</sub> > 0.6V for SGM852A<br>V <sub>SEN1</sub> > 0.6V, V <sub>SEN2</sub> < 0.55V for SGM852B | 0.925 | 1                   | 1.075 | μΑ    |  |  |  |

| OATE Output Valle on (1)                  |                          | V <sub>cc</sub> ≤ 5V                                                                                                                                                                                 | -10%  | 2 × V <sub>CC</sub> | +10%  |       |  |  |  |

| GATE Output Voltage (1)                   | $V_{GATE}$               | V <sub>cc</sub> > 5V                                                                                                                                                                                 | 9.0   | 10.0                | 11.0  | V     |  |  |  |

| C <sub>D_RST</sub> Trip Rising Threshold  | V <sub>RTH_RST</sub>     | AR W                                                                                                                                                                                                 | 1.191 | 1.234               | 1.277 | V     |  |  |  |

| C <sub>D_RST</sub> Hysteresis             | V <sub>HYS_RST</sub>     |                                                                                                                                                                                                      |       | 50                  |       | mV    |  |  |  |

| C <sub>D_GATE</sub> Trip Rising Threshold | V <sub>RTH_GATE</sub>    |                                                                                                                                                                                                      | 1.191 | 1.234               | 1.277 | V     |  |  |  |

| C <sub>D_GATE</sub> Hysteresis            | V <sub>HYS_GATE</sub>    |                                                                                                                                                                                                      |       | 50                  |       | mV    |  |  |  |

| C <sub>D_RST</sub> Discharging Resistor   |                          | I <sub>CD_RST</sub> = 10mA                                                                                                                                                                           |       | 7                   | 12    | Ω     |  |  |  |

| C <sub>D_GATE</sub> Discharging Resistor  |                          | I <sub>CD_GATE</sub> = 10mA                                                                                                                                                                          |       | 7                   | 12    | Ω     |  |  |  |

| Over-Temperature Protection               |                          |                                                                                                                                                                                                      |       |                     |       |       |  |  |  |

| Thermal Shutdown                          | T <sub>SD</sub>          |                                                                                                                                                                                                      |       | 155                 |       | °C    |  |  |  |

| Thermal Shutdown Hysteresis               | $\Delta T_{SD}$          |                                                                                                                                                                                                      |       | 20                  |       | °C    |  |  |  |

#### NOTE:

1. Note that when  $V_{GATE}$  is from 0V to 2 ×  $V_{CC}$  (or from 0V to 10V), it needs to go through several cycles, during which a large current will flow from the GATE pin.

## TYPICAL PERFORMANCE CHARACTERISTICS

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

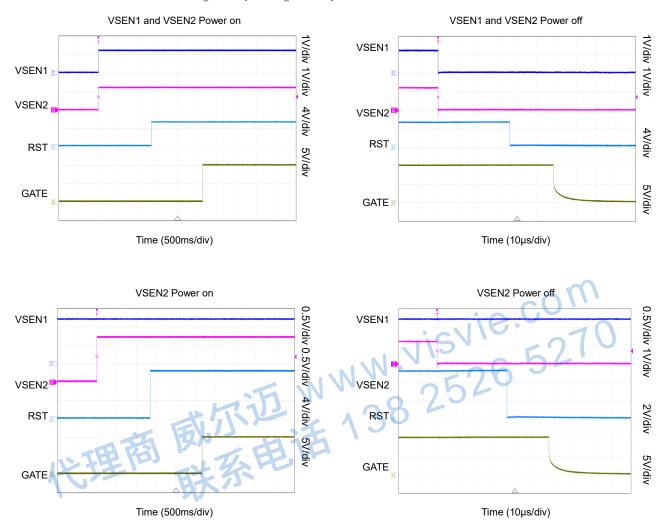

$V_{IN} = 16V$ ,  $C_{IN} = 100$ nF,  $C_{CP} = 47$ nF,  $C_{CD\_RST} = 1$  $\mu$ F,  $C_{CD\_GATE} = 1$  $\mu$ F,  $C_{GATE} = 1$ nF, VSEN1 = VSEN2 = 0V to 1.2V.

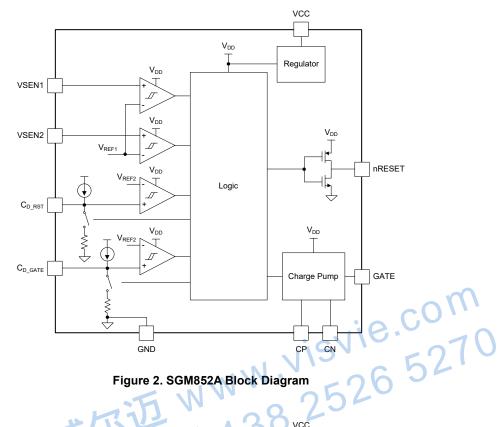

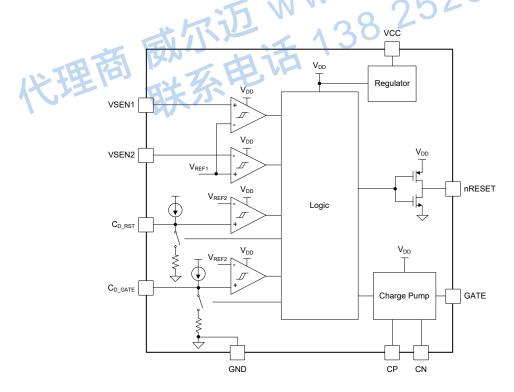

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. SGM852A Block Diagram

Figure 3. SGM852B Block Diagram

#### **DETAILED DESCRIPTION**

The SGM852 is used to monitor dual-voltage systems and provides sequential control with two outputs. When the power input voltage (V<sub>CC</sub>) exceeds the POR threshold voltage, V<sub>POR</sub> (2.6V, TYP), dual voltages are monitored through the respective external resistor dividers into VSEN1 and VSEN2 pin. Once both VSENx voltages exceed the internal fixed rising threshold,  $V_{RTH}$  (0.6V, TYP), in SGM852A or once VSEN1 exceeds V<sub>RTH</sub> and VSEN2 falls below the fixed falling threshold V<sub>FTH</sub>, (0.55V, TYP), in SGM852B, both internal comparators output high, the internal 1µA (TYP) current source I<sub>CD RST</sub> starts charging external capacitor at  $C_{D\ RST}$  pin. Once the voltage at  $C_{D\ RST}$  pin exceeds V<sub>RTH RST</sub> (1.234V, TYP), the nRESET outputs high and then another  $1\mu A$  (TYP) current source  $I_{CD\ GATE}$  starts charging external capacitor at C<sub>D GATE</sub> pin. Once the voltage at C<sub>D\_GATE</sub> pin exceeds V<sub>RTH\_GATE</sub> (1.234V, TYP), the GATE pin starts to drive an external N-MOSFET with a voltage level of 2  $\times$   $V_{DD}$ . Accordingly, the corresponding delay time can be programmed by choosing the capacitors at C<sub>D RST</sub> pin and C<sub>D GATE</sub> pin. If either of the two comparators outputs low, the nRESET outputs low and charge pump is disabled.

#### **Comparators**

The comparators can provide threshold voltage to monitor VSEN1 and VSEN2 sensing voltage, V<sub>VSEN1</sub> and V<sub>VSEN2</sub>. For SGM852A, both VSEN1 and VSEN2 are connected to the positive input of the corresponding comparator, while the internal reference is connected to the negative input of the two comparators. So when both VSEN1 and VSEN2 exceed  $\ensuremath{V_{\text{RTH}}},$  the nRESET outputs high after a C<sub>D RST</sub> controlled delay time. For SGM852B, VSEN1 is connected to the positive input of the comparator with the internal reference connecting to the negative input of the comparator, while VSEN2 is connected to the negative input of the comparator with the internal reference connecting to the positive input of the comparator. Therefore, for SGM852B, when VSEN1 exceeds  $V_{\text{RTH}}$  and VSEN2 falls below  $V_{\text{FTH}}$ , both comparators output high, and the nRESET outputs

high after a  $C_{D\_RST}$ -controlled delay time. If either of the comparators outputs low, the nRESET outputs low.

#### Power-On Reset (POR)

The device resets all fault latches and starts to monitor  $V_{VSEN1}$  and  $V_{VSEN2}$  once  $V_{CC}$  exceeds 2.6V.

#### **Charge Pump**

The charge pump with an internal oscillator is designed to drive external N-MOSFET with a voltage level of 2  $\times$  V<sub>DD</sub>.

#### Regulators

The input voltage of the SGM852 is range from 3V to 16V. The built-in regulator provides 5V internal  $V_{DD}$  if  $V_{CC}$  is above 5V, and it tracks  $V_{CC}$  if  $V_{CC}$  is below 5V.

#### **Push-Pull Reset Output**

The nRESET is a push-pull reset output pin. When both internal comparators output high, the nRESET asserts high after  $C_{D\_RST}$ -controlled delay time. And if either of the comparators outputs low, nRESET asserts low after  $C_{D\_RST}$  is discharged.

#### **GATE** Output

When nRESET asserts high, the charge pump is enabled after  $C_{D\_GATE}$ -controlled delay time. And then, GATE provides a voltage of 2 ×  $V_{DD}$  to drive the external N-MOSFET. If nRESET asserts low, the charge pump is disabled after  $C_{D\_GATE}$  discharged, and GATE will be discharged to 0V.

#### Over-Temperature Protection (OTP)

The SGM852 may heat up due to power dissipation, and then enter into the thermal shutdown state. The thermal shutdown threshold  $T_{\text{SD}}$  is +155°C (TYP). The OTP will turn off charge pump and timer function during this state. Accordingly, both nRESET and GATE output low. And the device will be shut down and remain off until the IC temperature drops below +135°C (TYP).

### **APPLICATION INFORMATION**

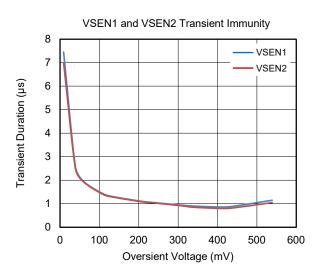

#### **VSENx Transient Immunity**

The VSEN1 and VSEN2 pins of the SGM852 have certain anti-interference ability. Once the transient duration exceeds the corresponding maximum allowed time, the nRESET pin will go low.

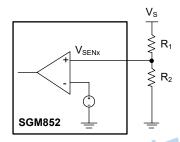

#### **Adjustable Input Sensing Threshold**

The dual sense inputs, VSEN1 and VSEN2, can monitor system voltage through a resistive divider network with  $V_{RTH}$  in a wide range. As shown in Figure 4,  $V_{S}$  is the system voltage. The trigger voltage of system  $V_{S}$  TH can be calculated by equation (1):

$$V_{S_{-}TH} = V_{TH} \times \left(1 + \frac{R_1}{R_2}\right) \tag{1}$$

Figure 4. Setting Trigger Voltage of System

The absolute maximum voltages of VSEN1 and VSEN2 are not allowed to exceed 3V. Due to the leakage currents of them are 100nA, the accuracy of  $V_{S\_TH}$  should be taken into consideration. However, low value resistor will cause more power consumption. Appropriate selection of resistance value is also very critical.

The appropriate resistance value can be selected through the following equation based on the amount of acceptable error.

$$R_{1} = \frac{V_{S_{-}TH} \times \varepsilon}{I_{SENSE}}$$

(2)

$V_{S\_TH}$  is the system trigger voltage that nRESET pin asserts high, and  $\epsilon$  is maximum acceptable error on  $V_{S\_TH}$ ,  $I_{SENSE}$  is the leakage current of VSEN1 and VSEN2 pins.  $R_2$  can be calculated by equation (3):

$$R_2 = \frac{V_{TH} \times R_1}{V_{S TH} - V_{TH}}$$

(3)

# Adjustable Delay ( $C_{D\_RST}$ , $C_{D\_GATE}$ )

Users should choose external capacitors to set the charge time from internal 1µA (TYP) current source and thus set nRESET and GATE pins output delay time. When the input voltage exceeds the POR threshold voltage, VSEN1 and VSEN2 pins will start to monitor system voltages. Once both outputs of the comparators are high, a 1µA (TYP) current source starts charging external capacitor at  $C_{D\_RST}$  pin. Once the voltage at  $C_{D\_RST}$  pin exceeds  $V_{RTH\_RST}$ , the nRESET outputs high and then another 1µA (TYP) current source starts charging external capacitor at  $C_{D\_GATE}$  pin. Once the voltage at  $C_{D\_GATE}$  pin exceeds  $V_{RTH\_GATE}$ , the GATE pin start to drive an external N-MOSFET with 2 ×  $V_{DD}$  voltage level by the charge pump circuit. The delay time can be calculated by equations (4) and (5):

$$t_{CD\_RST} = \frac{1.234V \times C_{CD\_RST}}{1\mu A}$$

(4)

$$t_{\text{CD\_GATE}} = \frac{1.234V \times C_{\text{CD\_GATE}}}{1\mu A} \tag{5}$$

where:

$t_{\text{CD\_RST}}$  and  $t_{\text{CD\_GATE}}$  are in seconds  $C_{\text{CD\_RST}}$  and  $C_{\text{CD\_GATE}}$  are in Farads.

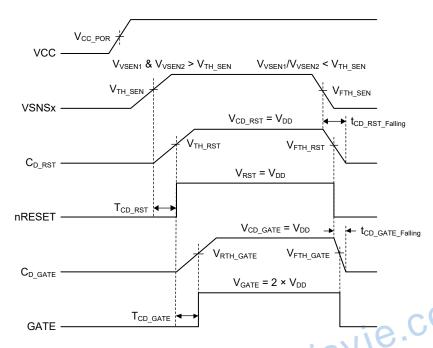

When either output of the comparators is low, the respective capacitors start to discharge on  $C_{D\_RST}$  and  $C_{D\_GATE}$  pins. Once the voltage level is lower than 1.184V (50mV Hysteresis, TYP), the nRESET and GATE go low. Figure 5 shows the time sequence.

# **APPLICATION INFORMATION (continued)**

NOTE: 1. V<sub>DD</sub> is only internally used. It tracks V<sub>CC</sub> if V<sub>CC</sub> is below 5V, and it is close to 5V if V<sub>CC</sub> is above 5V.

Figure 5. SGM852A Timing Sequence Diagram

### **Typical Application Circuits**

Figure 6. Power on Sequential Control Application Circuit of SGM852A

# **APPLICATION INFORMATION (continued)**

Figure 7. Drive N-MOSFET to Control Output Connection of SGM852A

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from | Original | (SEPTEMBER 2022) | to REV.A |

|--------------|----------|------------------|----------|

|              |          |                  |          |

Page

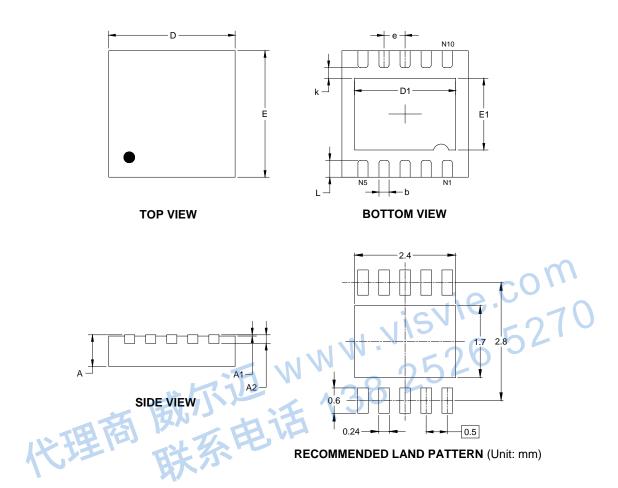

# PACKAGE OUTLINE DIMENSIONS TDFN-3×3-10L

| Symbol |           | nsions<br>meters | Dimensions<br>In Inches |       |  |

|--------|-----------|------------------|-------------------------|-------|--|

|        | MIN       | MAX              | MIN                     | MAX   |  |

| Α      | 0.700     | 0.800            | 0.028                   | 0.031 |  |

| A1     | 0.000     | 0.050            | 0.000                   | 0.002 |  |

| A2     | 0.203     | REF              | 0.008 REF               |       |  |

| D      | 2.900     | 3.100            | 0.114                   | 0.122 |  |

| D1     | 2.300     | 2.600            | 0.091                   | 0.103 |  |

| E      | 2.900     | 3.100            | 0.114                   | 0.122 |  |

| E1     | 1.500     | 1.800            | 0.059                   | 0.071 |  |

| k      | 0.200     | MIN              | 0.008 MIN               |       |  |

| b      | 0.180     | 0.300            | 0.007                   | 0.012 |  |

| е      | 0.500 TYP |                  | 0.020 TYP               |       |  |

| L      | 0.300     | 0.500            | 0.012                   | 0.020 |  |

NOTE: This drawing is subject to change without notice.

# TAPE AND REEL INFORMATION

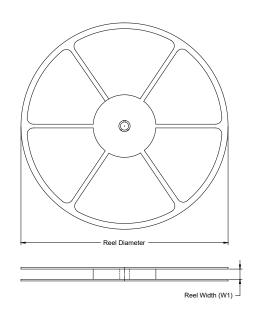

#### **REEL DIMENSIONS**

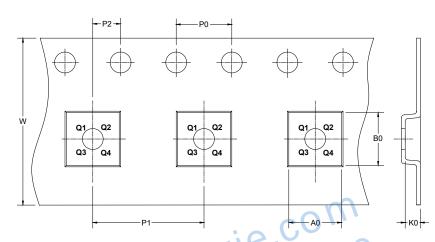

#### **TAPE DIMENSIONS**

DIRECTION OF FEED

NOTE: The picture is only for reference. Please make the object as the standard.

# KEY PARAMETER LIST OF TAPE AND REEL

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TDFN-3×3-10L | 13"              | 12.4                     | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

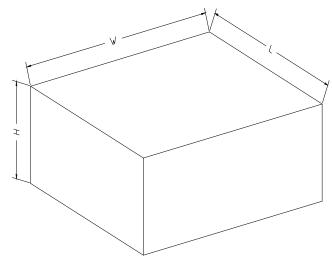

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| NOTE. THE plotare is of          | ny tor rotoronoo | . I loudo mako t | no object de un | o otanidara. | m       |  |  |  |  |

|----------------------------------|------------------|------------------|-----------------|--------------|---------|--|--|--|--|

| KEY PARAMETER LIST OF CARTON BOX |                  |                  |                 |              |         |  |  |  |  |

| Reel Type                        | Length<br>(mm)   | Width<br>(mm)    | Height<br>(mm)  | Pizza/Carton | 26 5210 |  |  |  |  |

| 7" (Option)                      | 368              | 227              | 224             | 082          | 020     |  |  |  |  |

| 7"                               | 442              | 410              | 224             | 18           |         |  |  |  |  |

| 13"                              | 386              | 280              | 370             | 5            | DD0002  |  |  |  |  |