### Dec. 2021 V1.7

# AW32001A Single Cell Li-ion Battery Charger with Power Path Management and Full USB Compliance

### **Features**

- Charge Voltage Regulation Accuracy:

±0.5% ( 0°C to 50°C )

- Charge Current Accuracy: ±5%

- Maximum 28V Input Voltage Rating with Over-Voltage Protection

- Minimum -5V Input Voltage Protection

- Complete Charge Process with Pre-Charge, Fast Charge and Constant Voltage Regulation

- Programmable Charge Parameters Through I<sup>2</sup>C Compatible Interface

- Programmable Charge Termination and Autonomous Recharge

- Wide Range of Fast Charge Current: 2mA~500mA

- Strong and Robust Protection: V<sub>IN</sub> OVP, Battery OVP, OCP, Reverse Leakage Protection, Short Protection, Thermal Protection, PCB Over Temperature Protection

- BATFET Control to Support Shipping Mode

- System Reset Function

- Fully Integrated Power Path Management

- Ultra-low Battery Leakage Current to Support Shipping Mode

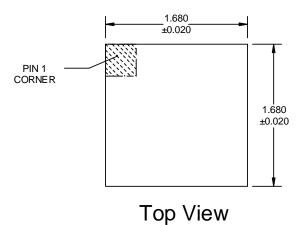

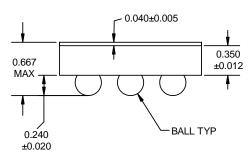

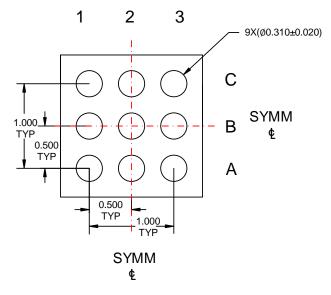

- WLCSP 1.68mm×1.68mm×0.63mm-9B, 0.5mm

Pitch Package

- 7-bit slave address (A7~A1) is 1001001 binary(0x49H)

- IEC62368-1 Approved-File No.BE-37454

# **Applications**

- Smart Handheld Devices

- Wearable Devices

- Smart Watches

- Fitness Accessories

### **General Description**

The AW32001A is a highly-integrated Li-Ion/Li-Polymer battery linear charger with system power path management. The charge process of AW32001A includes: Pre-Charge, Fast Charge and Constant Voltage Regulation. The charge parameters and operating modes programmable through I2C interface. The charge process runs automatically and recharging occurs when the battery voltage drops below VBAT\_REG-VRECH after the charge done status.

The AW32001A is targeted at space limited portable applications. The chip can take input power from either an AC adaptor or a USB port to supply the system load and charge the battery. Meanwhile, the chip provides system short circuit protection function by limiting the current from the input to the system and the battery to the system. These features are effective to protect the battery or chip from damage. The parameters of input current limit, the discharge current limit and safety timer can be programmed by the I<sup>2</sup>C interface. Additionally, input over voltage protection, input under voltage lockout and input headroom voltage are integrated for good input source detection.

AW32001A separates the charging route from the system power supply to fulfill the power management function. The system power supply is at first priority with no dependency on battery existence. Once a bad power-limited adapter appears at the input, AW32001A would reduce the charging current firstly. If the system load is still too heavy for input source, AW32001A will reduce the input-system current to prevent the input source from being pulled down. Under this circumstance, if the system voltage drops 30mV below the battery voltage, the battery to system supply route will be fully turned on to power the system load, which is supplement mode.

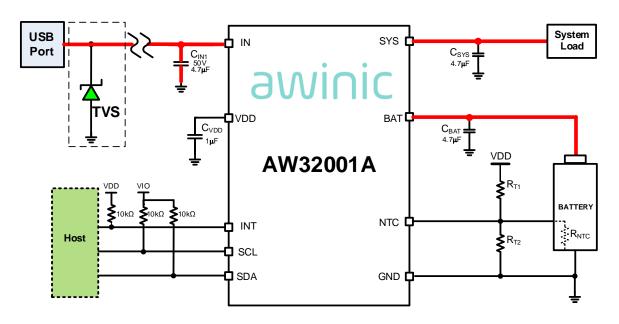

# Typical Application Circuit

Figure 1 Typical Application Circuit of AW32001A

All trademarks are the property of their respective owners.

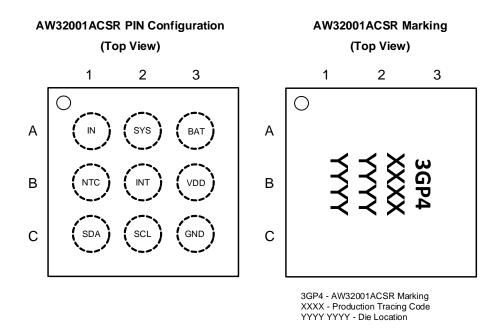

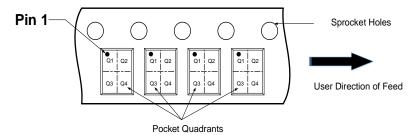

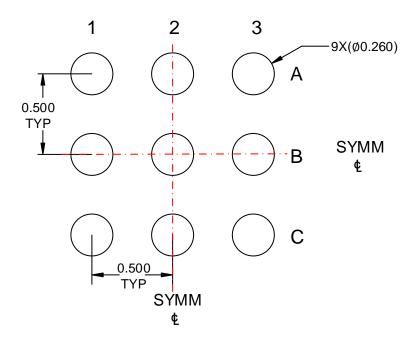

# **Pin Configuration and Top Mark**

Figure 2 Pin Configuration and Top Mark

# **Pin Definition**

| Pin No. | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | IN       | Input power pin. Bypass with a 4.7µF capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                 |

| A2      | SYS      | System power supply pin. Bypass with a 4.7µF capacitor to GND.                                                                                                                                                                                                                                                                                                                                                         |

| A3      | BAT      | Battery pin. Bypass with a 4.7µF capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                     |

| B1      | NTC      | Temperature sense input. Connect a negative temperature coefficient thermistor. Program the hot and cool temperature window with resistor dividers from VDD to GND, and NTC is the middle node. Pull NTC to VDD if NTC function is not used. If NTC function is unused, it is suggested to disable the NTC function and tie the NTC port to VDD for decreasing leakage current of battery, because PCB_OTP is default. |

| B2      | INT      | Interrupt output. The INT pin can send charge status and fault interrupt to the host. This pin is also used to disconnect the system from battery, and awake the chip from shipping mode. If INT is unused, it is suggested to tie INT to VDD by resistor.                                                                                                                                                             |

| В3      | VDD      | Internal power supply pin. Bypass with a 1µF capacitor to GND. No external load is allowed.                                                                                                                                                                                                                                                                                                                            |

| C1      | SDA      | I <sup>2</sup> C Interface serial date.                                                                                                                                                                                                                                                                                                                                                                                |

| C2      | SCL      | I <sup>2</sup> C Interface clock.                                                                                                                                                                                                                                                                                                                                                                                      |

| C3      | GND      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                |

# **Ordering Information**

| Part<br>Number | Temperature | Package                   | Marking | Moisture<br>Sensitivity<br>Level | Environmental Information | Delivery<br>Form                |

|----------------|-------------|---------------------------|---------|----------------------------------|---------------------------|---------------------------------|

| AW32001ACSR    | -40°C∼85°C  | WLCSP<br>1.68mm×1.68mm-9B | 3GP4    | MSL1                             | ROHS+HF                   | 3000 units/<br>Tape and<br>Reel |

# **Absolute Maximum Ratings**(NOTE1)

| PARAMETERS                                                |                                      |      | MAX                   | UNIT |

|-----------------------------------------------------------|--------------------------------------|------|-----------------------|------|

| Input voltage range V <sub>IN</sub> (with respect to GND) | IN                                   | -5   | 28                    | V    |

| NTC voltage range V <sub>NTC</sub> (with respect to GND)  | NTC                                  | -0.3 | V <sub>VDD</sub> +0.3 | V    |

| Other pins voltage range (with respect to GND)            | SYS, BAT, INT, VDD,<br>SCL, SDA      | -0.3 | 6                     | V    |

| Operating free-air temperature range                      | Operating free-air temperature range |      |                       | °C   |

| Operating junction temperature T <sub>J</sub>             |                                      |      | 150                   | °C   |

| Storage temperature T <sub>STG</sub>                      |                                      |      | 150                   | °C   |

| Lead temperature (Soldering 10 seconds)                   |                                      |      | 260                   | °C   |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

# **ESD Rating and Latch Up**

| PARAMETERS                      | VALUE     | UNIT |

|---------------------------------|-----------|------|

| HBM (Human Body Model) (NOTE 2) | ±2        | kV   |

| CDM(NOTE 3)                     | ±1.5      | kV   |

| Lotob Lip(NOTE 4)               | +IT: 200  | mΛ   |

| Latch-Up <sup>(NOTE 4)</sup>    | -IT: -200 | mA   |

NOTE2: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test

method: ESDA/JEDEC JS-001-2017

NOTE3: Test method: ESDA/JEDEC JS-002-2018

NOTE4: Test method: JESD78E

# **Recommended Operating Conditions**

| PARAMETERS                                     | MIN | NORM | MAX   | UNIT |

|------------------------------------------------|-----|------|-------|------|

| Supply voltage range V <sub>IN</sub>           | 4   |      | 5.5   | V    |

| Supply current I <sub>IN</sub>                 |     |      | 550   | mA   |

| Discharge current I <sub>BAT</sub>             |     |      | 3.2   | Α    |

| Charge current I <sub>CHG</sub>                | 2   |      | 512   | mA   |

| Battery regulated voltage V <sub>BAT_REG</sub> | 3.6 |      | 4.545 | V    |

| Operating junction temperature T <sub>J</sub>  | -40 |      | 125   | °C   |

# **Thermal Information**

| PARAMETERS                                           | VALUE | UNIT |

|------------------------------------------------------|-------|------|

| Junction-to-ambient thermal resistance $\theta_{JA}$ | 122   | °C/W |

# **Electrical Characteristics**

$V_{IN}$ =5V,  $V_{BAT}$ =3.5V,  $T_J$ =25°C for typical values (unless otherwise noted).

|                       | PARAMETER                                                         | TEST CONDITIONS                                                                          | MIN   | TYP   | MAX   | UNIT |

|-----------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|-------|-------|------|

| INPUT SO              | OURCE AND BATTERY PROT                                            | TECTION                                                                                  | •     | •     | •     |      |

| VIN_UVLO              | UVLO threshold voltage, entry UVLO                                | V <sub>IN</sub> falling                                                                  | 3.5   | 3.6   | 3.7   | V    |

|                       | Hysteresis for UVLO                                               | V <sub>IN</sub> rising                                                                   |       | 300   |       | mV   |

| T <sub>DGL_UVLO</sub> | Exit Deglitch time for VIN UVLO                                   | Exits VIN UVLO                                                                           |       | 30    |       | ms   |

|                       | VIN OVP threshold voltage                                         | V <sub>IN</sub> rising                                                                   | 5.85  | 6     | 6.15  | V    |

| V <sub>IN_OVP</sub>   | VIN OVP hysteresis                                                | V <sub>IN</sub> falling from above V <sub>IN_OVP</sub>                                   |       | 350   |       | mV   |

| T <sub>DGL_OVP</sub>  | Exit deglitch time for V <sub>IN_OVP</sub>                        | Exits VIN OVP                                                                            |       | 30    |       | ms   |

| V <sub>BAT</sub>      | BAT input voltage                                                 |                                                                                          |       |       | 4.6   | V    |

|                       | 10/10/11                                                          | REG01H[2:0]=000                                                                          | 2.33  | 2.43  | 2.53  | V    |

| V                     | UVLO threshold voltage for BAT voltage, V <sub>BAT</sub> falling, | REG01H[2:0]=100                                                                          | 2.64  | 2.76  | 2.88  | V    |

| VBAT_UVLO             | entry UVLO                                                        | REG01H[2:0]=111                                                                          | 2.93  | 3.03  | 3.13  | V    |

|                       | Hysteresis voltage                                                | V <sub>BAT_UVLO</sub> =2.76V                                                             |       | 190   |       | mV   |

| VHDRM                 | Input vs. battery voltage headroom threshold                      | V <sub>IN</sub> rising                                                                   | 80    | 130   | 170   | mV   |

|                       | Input vs. battery voltage headroom threshold hysteresis           | V <sub>IN</sub> falling                                                                  |       | 60    |       | mV   |

| CHARGE                | PROCESS                                                           |                                                                                          |       |       |       |      |

|                       | Pre-charge to fast charge                                         | REG04H[1]=1, V <sub>BAT</sub> rising                                                     | 2.9   | 3.0   | 3.1   | V    |

| $V_{BAT\_PRE}$        | threshold                                                         | REG04H[1]=0, V <sub>BAT</sub> rising                                                     | 2.7   | 2.8   | 2.9   | V    |

|                       | Fast charge to pre-charge threshold                               | V <sub>BAT</sub> falling                                                                 |       | 200   |       | mV   |

|                       |                                                                   | REG04H[7:2]=000000,<br>V <sub>BAT_REG</sub> =3.6V                                        | 3.585 | 3.600 | 3.615 | V    |

| .,                    | Battery charge voltage                                            | REG04H[7:2]=101000,<br>V <sub>BAT_REG</sub> =4.2V                                        | 4.180 | 4.200 | 4.220 | V    |

| V <sub>BAT_REG</sub>  | regulation voltage                                                | REG04H[7:2]=110100,<br>V <sub>BAT_REG</sub> =4.38V                                       | 4.360 | 4.380 | 4.400 | V    |

|                       |                                                                   | REG04H[7:2]=111110,<br>V <sub>BAT_REG</sub> =4.53V                                       | 4.507 | 4.530 | 4.553 | V    |

|                       |                                                                   | REG04H[0]=0, V <sub>BAT_REG</sub> =4.2V,<br>below V <sub>BAT_REG</sub>                   | 60    | 100   | 140   | mV   |

| V <sub>RECH</sub>     | Recharge threshold voltage                                        | REG04H[0]=1, V <sub>BAT_REG</sub> =4.2V,<br>below V <sub>BAT_REG</sub>                   | 160   | 200   | 240   | mV   |

|                       | Deglitch time for V <sub>RECH</sub>                               | V <sub>BAT</sub> falling below V <sub>RECH</sub> after charge termination                |       | 130   |       | ms   |

| M                     | Battery OVP threshold voltage                                     | V <sub>BAT</sub> threshold over V <sub>BAT_REG</sub> to turn off charger during charging |       | 130   |       | mV   |

| V <sub>BAT_OVP</sub>  | V <sub>BAT_OVP</sub> hysteresis                                   |                                                                                          |       | 50    |       | mV   |

|                       | 1                                                                 | 1                                                                                        | L     | 1     | 1     |      |

# **Electrical Characteristics (Continued)**

$V_{IN}$ =5V,  $V_{BAT}$ =3.5V,  $T_J$ =25°C for typical values (unless otherwise noted).

| PARAMETER            |                                                                      | TEST CONDITIONS                                                                                                          | MIN  | TYP  | MAX  | UNIT |

|----------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| POWER P              | ATH MANAGEMENT                                                       | ,                                                                                                                        |      | •    |      |      |

|                      |                                                                      | V <sub>IN</sub> =5.0V, REG07H[3:0]=0000,<br>R <sub>SYS</sub> =100Ω, I <sub>CHG</sub> =0A,<br>V <sub>SYS_REG</sub> =4.2V  | 4.11 | 4.20 | 4.29 | V    |

| V <sub>SYS_REG</sub> | Regulated system output voltage                                      | $V_{IN}$ =5.0V, REG07H[3:0]=1000, R <sub>SYS</sub> =100 $\Omega$ , I <sub>CHG</sub> =0A, V <sub>SYS_REG</sub> =4.6V      | 4.51 | 4.60 | 4.69 | V    |

|                      |                                                                      | V <sub>IN</sub> =5.3V, REG07H[3:0]=1111,<br>R <sub>SYS</sub> =100Ω, I <sub>CHG</sub> =0A,<br>V <sub>SYS_REG</sub> =4.95V | 4.85 | 4.95 | 5.05 | V    |

|                      |                                                                      | REG00H[3:0]=0000, I <sub>IN_LIM</sub> =50mA                                                                              | 30   | 45   | 60   | mA   |

| ı                    | land to a company time it                                            | REG00H[3:0]=0011, I <sub>IN_LIM</sub> =140mA                                                                             | 112  | 125  | 140  | mA   |

| I <sub>IN_LIM</sub>  | Input current limit                                                  | REG00H[3:0]=1001, I <sub>IN_LIM</sub> =320mA                                                                             | 275  | 296  | 320  | mA   |

|                      |                                                                      | REG00H[3:0]=1111, I <sub>IN_LIM</sub> =500mA                                                                             | 440  | 460  | 500  | mA   |

|                      |                                                                      | REG00H[7:4]=0000, V <sub>IN_DPM</sub> =3.88V                                                                             | 3.68 | 3.88 | 4.18 | V    |

| VIN_DPM              | Dynamic input power management clamp                                 | REG00H[7:4]=1000, V <sub>IN_DPM</sub> =4.52V                                                                             | 4.32 | 4.52 | 4.82 | V    |

|                      | voltage                                                              | REG00H[7:4]=1111, V <sub>IN_DPM</sub> =5.08V                                                                             | 4.88 | 5.08 | 5.35 | V    |

| Ron_Q1               | IN to SYS switches on resistance                                     | V <sub>IN_DPM</sub> =3.88V, V <sub>IN</sub> =4.5V,<br>I <sub>SYS</sub> =100mA                                            |      | 300  | 350  | mΩ   |

| Ron_q2               | BAT to SYS switch on resistance                                      | V <sub>IN</sub> <2V, V <sub>BAT</sub> =3.5V, I <sub>SYS</sub> =100mA                                                     |      | 103  | 115  | mΩ   |

|                      | Input quiescent current (not include the current                     | V <sub>IN</sub> =5V, EN_HIZ=0, CEB=0,<br>(charge enable), I <sub>CHG</sub> =0, I <sub>SYS</sub> =0                       |      | 1.7  | 3.2  | mA   |

| lin_q                | from external NTC resistor)                                          | V <sub>IN</sub> =5V, EN_HIZ=0, CEB=1, (charge disabled), I <sub>CHG</sub> =0, I <sub>SYS</sub> =0                        |      | 1.5  | 3.0  | mA   |

|                      |                                                                      | V <sub>IN</sub> =5V, CEB=0, charge done,<br>I <sub>CHG</sub> =0, I <sub>SYS</sub> =0                                     |      | 58   | 80   | μΑ   |

|                      |                                                                      | V <sub>IN</sub> =0, CEB=1, V <sub>BAT</sub> =4.35V,<br>DIS PCB OTP=1, I <sub>SYS</sub> =0                                |      | 21   | 32   | μΑ   |

| I <sub>BAT_Q</sub>   | Battery quiescent current (not include the current from external NTC | V <sub>IN</sub> =0, CEB=1, V <sub>BAT</sub> =4.35V,<br>DIS_PCB_OTP=0, I <sub>SYS</sub> =0                                |      | 27   | 38   | μΑ   |

|                      | resistor)                                                            | V <sub>IN</sub> =0, CEB=1, V <sub>BAT</sub> =4.35V,<br>DIS_PCB_OTP=0, I <sub>SYS</sub> =0, enable<br>watchdog            |      | 28   | 38   | μΑ   |

|                      |                                                                      | V <sub>BAT</sub> =4.5V, V <sub>IN</sub> =V <sub>SYS</sub> =0,<br>FET_DIS=1, shipping mode                                |      |      | 1    | μΑ   |

| Isys-bat_lkg         | SYS reverse to BAT switch leakage                                    | V <sub>SYS</sub> =4.60V, V <sub>IN</sub> =5V, V <sub>BAT</sub> =0,<br>CEB=1, EN_HIZ=1, charge<br>disabled                |      |      | 1    | μΑ   |

| I <sub>DSCHG</sub>   | BAT FET discharge                                                    | REG03H[7:4]=0001, I <sub>DSCHG</sub> =400mA                                                                              | 300  | 440  | 500  | mA   |

| ישטכחט               | current limit                                                        | REG03H[7:4]=1001,I <sub>DSCHG</sub> =2000mA                                                                              |      | 2000 |      | mA   |

| V <sub>FWD</sub>     | Ideal diode forward voltage in supplement mode                       | 50mA discharge current                                                                                                   |      | 30   |      | mV   |

# **Electrical Characteristics (Continued)**

$V_{\text{IN}}$ =5V,  $V_{\text{BAT}}$ =3.5V,  $T_{\text{J}}$ =25°C for typical values (unless otherwise noted)

|                        | PARAMETER                                                   | TEST CONDITIONS                                                                                                                 | MIN | TYP | MAX | UNIT |

|------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| CHARGE                 | CURRENT                                                     |                                                                                                                                 |     |     |     |      |

|                        |                                                             | V <sub>BAT_PRE</sub> <v<sub>BAT<v<sub>BAT_REG ,<br/>REG0BH[7]=1, I<sub>CHG</sub>=2mA</v<sub></v<sub>                            | 1.5 | 2   | 2.5 | mA   |

|                        |                                                             | VBAT_PRE <vbat<vbat_reg ,<br="">REG0BH[7]=0, Ichg=8mA</vbat<vbat_reg>                                                           | 6.9 | 8   | 9   | mA   |

|                        | Output charge regulation current programmable range         | VBAT_PRE <vbat<vbat_reg ,="" ichg="96mA&lt;/td" reg0bh[7]="0,"><td>89</td><td>96</td><td>103</td><td>mA</td></vbat<vbat_reg>    | 89  | 96  | 103 | mA   |

|                        |                                                             | VBAT_PRE <vbat<vbat_reg ,="" ichg="264mA&lt;/td" reg0bh[7]="0,"><td>252</td><td>264</td><td>276</td><td>mA</td></vbat<vbat_reg> | 252 | 264 | 276 | mA   |

| I <sub>CHG</sub>       |                                                             | V <sub>BAT_PRE</sub> <v<sub>BAT<v<sub>BAT_REG ,<br/>REG0BH[7]=0, I<sub>CHG</sub>=456mA</v<sub></v<sub>                          | 434 | 456 | 478 | mA   |

|                        |                                                             | V <sub>BAT</sub> =3.8V, I <sub>CHG</sub> =2mA                                                                                   | -25 |     | 25  | %    |

|                        | Charge Current Regulation                                   | V <sub>BAT</sub> =3.8V, 4mA <i<sub>CHG≤12mA</i<sub>                                                                             | -20 |     | 20  | %    |

|                        | Accuracy                                                    | V <sub>BAT</sub> =3.8V,12mA <i<sub>CHG&lt;264mA</i<sub>                                                                         | -7  |     | 7   | %    |

|                        |                                                             | V <sub>BAT</sub> =3.8V, I <sub>CHG</sub> ≥264mA                                                                                 | -5  |     | 5   | %    |

| I <sub>PRE</sub>       | Pre-charge current programmable range, IPRE=ITERM           | V <sub>BAT</sub> <3.0V                                                                                                          | 1   |     | 31  | mA   |

|                        | Termination charge current threshold, programmable          | REG03H[3:0]=0000,<br>I <sub>CHG</sub> =1mA                                                                                      | 0.8 | 1   | 1.2 | mA   |

|                        |                                                             | REG03H[3:0]=0001,<br>I <sub>CHG</sub> =3mA                                                                                      | 2.6 | 3   | 3.3 | mA   |

| ITERM                  |                                                             | REG03[3:0]=0101,<br>I <sub>CHG</sub> =11mA                                                                                      | 9.5 | 11  | 13  | mA   |

|                        |                                                             | REG03H[3:0]=1111,<br>I <sub>CHG</sub> =31mA                                                                                     | 28  | 31  | 34  | mA   |

| T <sub>TERM</sub>      | Termination deglitch time                                   | I <sub>CHG</sub> <i<sub>TERM, REG0CH[6]=0</i<sub>                                                                               |     | 3.2 |     | s    |

| I <sub>DBAT</sub>      | Battery detection current before charge done (sink current) | Begins after termination                                                                                                        |     | 0.5 |     | mA   |

| T <sub>DBAT</sub>      | Battery detection time                                      | detected and V <sub>BAT</sub> < V <sub>BAT_REG</sub>                                                                            |     | 262 |     | ms   |

| INT                    |                                                             |                                                                                                                                 |     |     |     |      |

| V <sub>OL_INT</sub>    | Low-level output saturation voltage, INT pin                | Io=5mA, sink current                                                                                                            |     |     | 0.4 | V    |

| ILKG_INT               | High-level leakage current for INT                          | INT is in High-impedance status, V <sub>INT</sub> =5V                                                                           |     |     | 1   | μΑ   |

| T <sub>RST_DGL</sub>   | INT pulled low time to reset V <sub>SYS</sub>               | V <sub>INT</sub> low(default setting)                                                                                           |     | 16  |     | s    |

| I <sup>2</sup> C BUS L | OGIC LEVELS AND TIMING CH                                   | IARACTERISITICS                                                                                                                 |     |     |     |      |

| VoL                    | Output low threshold level                                  | Io=5mA, sink current                                                                                                            |     |     | 0.4 | V    |

| V <sub>IL</sub>        | Input low threshold level                                   | V <sub>pull_up</sub> =1.8V, SDA, SCL and INT                                                                                    |     |     | 0.4 | V    |

| VIH                    | Input high threshold level                                  | V <sub>pull_up</sub> =1.8V, SDA, SCL and INT                                                                                    | 1.3 |     |     | V    |

|                    | PARAMETER                                   | TEST CONDITIONS                         | MIN | TYP | MAX | UNIT |

|--------------------|---------------------------------------------|-----------------------------------------|-----|-----|-----|------|

| I <sub>BIAS</sub>  | Input bias current                          | V <sub>pull_up</sub> =1.8V, SDA and SCL |     |     | 1   | μA   |

| THERMAL F          | PROTECTION                                  |                                         | 1   | •   | •   | •    |

| T <sub>J_REG</sub> | Junction temperature regulation             | Junction temperature rising             |     | 120 |     | °C   |

| т.                 | Overheating shutdown protection temperature | Junction temperature rising             |     | 150 |     | °C   |

| Тотр               | Thermal hysteresis for Totp                 | Junction temperature falling            |     | 20  |     | °C   |

| Into               | NTC pin output current                      | CEB=0, NTC=3V                           | -1  | 0   | 1   | μA   |

| \/                 | NTC cool temp rising threshold              | Percentage of VDD                       | 62  | 64  | 66  | %    |

| Vcool              | Hysteresis voltage                          |                                         |     | 60  |     | mV   |

| Vнот               | NTC hot temp falling threshold              | Percentage of VDD                       | 31  | 33  | 35  | %    |

|                    | Hysteresis voltage                          |                                         |     | 70  |     | mV   |

|                    | NTC hot temp falling threshold for PCB OTP  | Percentage of VDD                       | 31  | 33  | 35  | %    |

| VHOT_PCB           | Hysteresis voltage                          |                                         |     | 70  |     | mV   |

| SHIPPING N         | NODE EXIT TIME                              |                                         | ·   |     |     |      |

|                    | VOLIO DI                                    | REG0BH[0]=0                             | 1.8 | 2   | 3.3 | s    |

| <b>T</b>           | VBUS Plug in                                | REG0BH[0]=1                             | 90  | 100 | 111 | ms   |

| Texit_shipmode     | Dot down INT DIN                            | REG22H[3]=0                             | 1.8 | 2   | 3.3 | s    |

|                    | Put down INT PIN                            | REG22H[3]=1                             | 90  | 100 | 111 | ms   |

| CLOCK FRE          | EQUENCY AND WATCHDOG                        | TIMER                                   | •   |     | •   |      |

| F <sub>CLK</sub>   | Clock frequency                             |                                         |     | 250 |     | KHz  |

| t <sub>WDT</sub>   | Watchdog timer                              | REG05H[6:5]=11                          |     | 160 |     | s    |

# **Electrical Characteristics (Continued)**

$V_{\text{IN}}$ =5V,  $V_{\text{BAT}}$ =3.5V,  $T_{\text{J}}$ =25°C for typical values (unless otherwise noted)

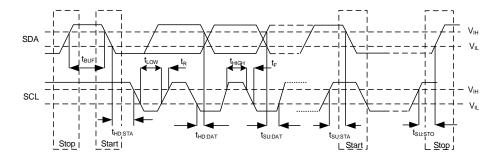

### I<sup>2</sup>C INTERFACE TIMING

| SYMBOL           | DESCRIPTION                               |     | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------------------|-----|-----|-----|-----|------|

| F <sub>SCL</sub> | Interface Clock Frequency                 |     |     |     | 400 | kHz  |

| _                | De alife la Tirre                         | SCL |     | 83  |     | ns   |

| TDEGLITCH        | Deglitch Time                             | SDA |     | 115 |     | ns   |

| thd:sta          | (Repeat-Start) Start Condition Hold Time  |     | 0.6 |     |     | μs   |

| tLOW             | Low Level Width of SCL                    |     | 1.3 |     |     | μs   |

| tнівн            | High Level Width of SCL                   |     | 0.6 |     |     | μs   |

| tsu:sta          | (Repeat-Start) Start Condition Setup Time |     | 0.6 |     |     | μs   |

| thd:dat          | Data Hold Time                            |     | 0   |     |     | μs   |

| tsu:dat          | Data Setup Time                           |     | 0.1 |     |     | μs   |

| t <sub>R</sub>   | Rising Time of SDA and SCL                |     |     |     | 0.3 | μs   |

| t <sub>F</sub>   | Falling Time of SDA and SCL               |     |     |     | 0.3 | μs   |

| tsu:sto          | Stop Condition Setup Time                 |     | 0.6 |     |     | μs   |

| tBUF             | Time Between Start and Stop Condition     |     | 1.3 |     |     | μs   |

Figure 3 I<sup>2</sup>C Interface Timing

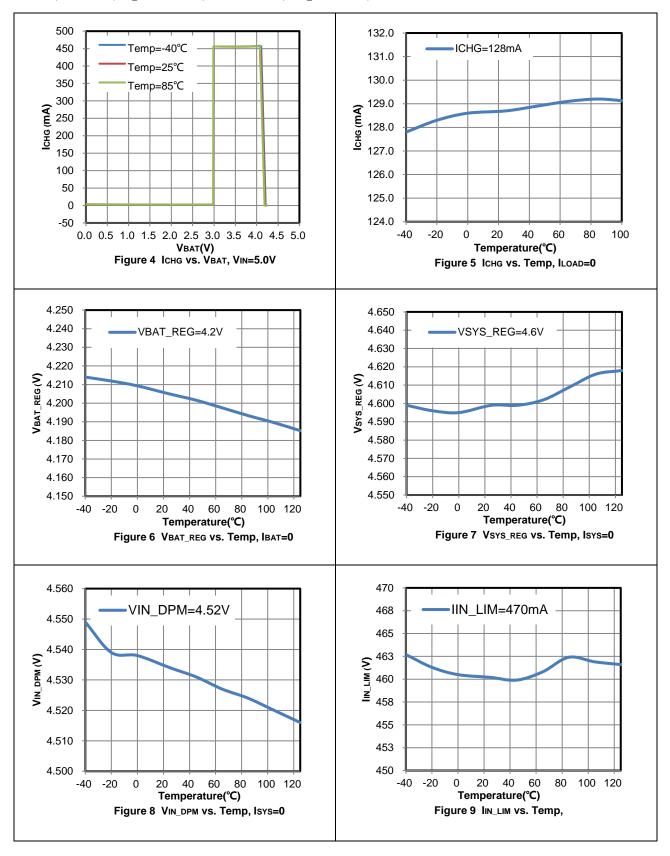

# **Typical Characteristics**

$V_{\text{IN}}\!=\!5V,\,T_{\text{J}}\!=\!25^{\circ}C,\,I_{\text{IN}\_\text{LIM}}\!=\!500\text{mA},\,I_{\text{CHG}}\!=\!128\text{mA},\,V_{\text{IN}\_\text{DPM}}\!=\!4.6V,\,\text{unless other noted}.$

# **Typical Characteristics**

$V_{IN}\!\!=\!\!5V,\,T_{J}\!\!=\!\!25^{\circ}C,\,I_{IN\_LIM}\!\!=\!\!500mA,\,I_{CHG}\!\!=\!\!128mA,\,V_{IN\_DPM}\!\!=\!\!4.6V,\,unless\,other\,noted.$

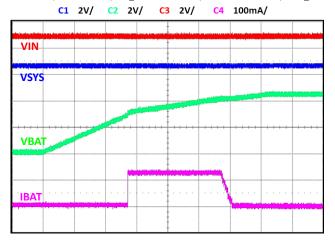

Isys=0A

Battery Charge Curve

I<sub>SYS</sub>=0A

Auto-Recharge Curve

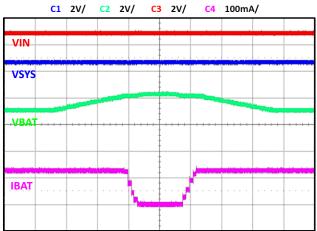

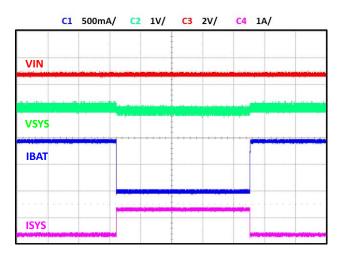

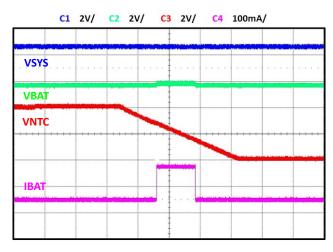

V<sub>BAT</sub>=3.7V Input Current Limit-Based PPM

V<sub>IN</sub>=5V/200mA, V<sub>BAT</sub>=3.7V Input Voltage Regulation-Based PPM

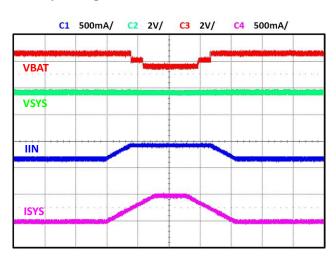

$V_{\text{IN}=5}V$ ,  $V_{\text{BAT}=3.7}V$ ,  $I_{\text{CHG}=456}mA$ ,  $I_{\text{SYS}=0}A\sim1A$  SYS Load Transient

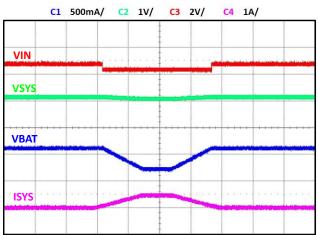

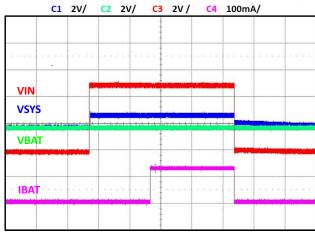

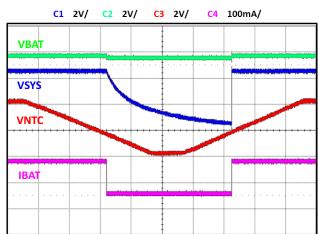

V<sub>BAT</sub>=3.7V, I<sub>SYS</sub>=0A **Power On/Off**

## **Typical Characteristics (Continued)**

$V_{IN}\!\!=\!\!5V,\,T_{J}\!\!=\!\!25^{\circ}C,\,I_{IN\_LIM}\!\!=\!\!500mA,\,I_{CHG}\!\!=\!\!128mA,\,V_{IN\_DPM}\!\!=\!\!4.6V,\,unless\,other\,noted.$

V<sub>BAT</sub>=3.7V, I<sub>SYS</sub>=0A Charge Enable/Disable

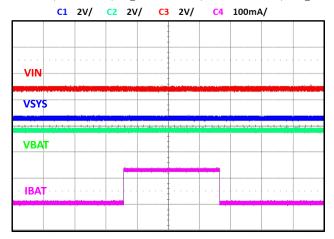

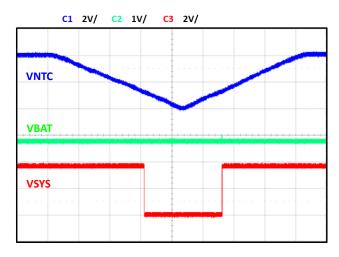

$\label{eq:Vbat} V_{\text{BAT}} {=} 3.7 \text{V, } I_{\text{SYS}} {=} 0 \text{A, PCB\_OTP disabled} \\ \textbf{NTC Rising}$

$V_{BAT}$ =3.7V,  $I_{SYS}$ =0A, PCB\_OTP disabled NTC Falling

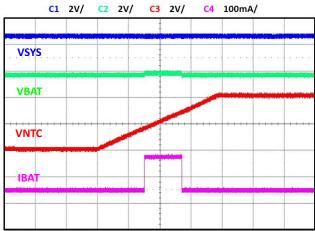

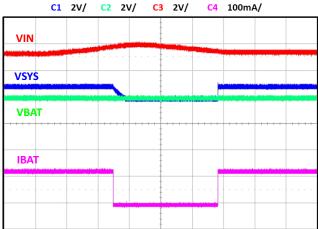

V<sub>BAT</sub>=3.7V, I<sub>SYS</sub>=0A

PCB\_OTP @Charge mode

V<sub>IN</sub>=0V, V<sub>BAT</sub>=3.7V PCB\_OTP @Discharge mode

$\label{eq:Vbat} \begin{array}{l} V_{\text{BAT}} {=} 3.7 V, \ I_{\text{SYS}} {=} 0 A \\ V_{\text{IN}} \ \text{OVP Operation} \end{array}$

# **Functional Diagram**

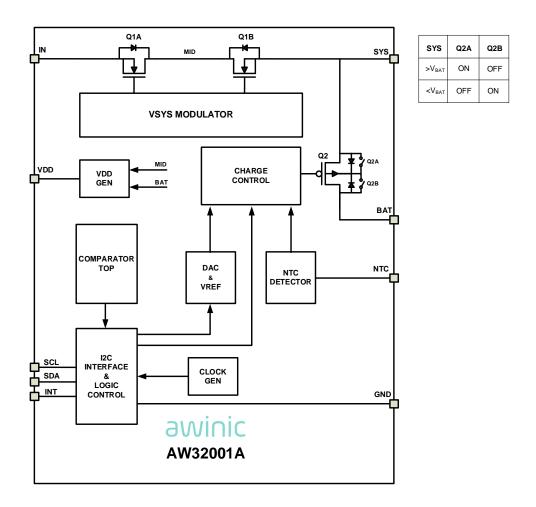

Figure 10 Functional Block Diagram

### **Detailed Functional Description**

The AW32001A is a highly integrated linear battery charger with a complete power path management function (PPMF). The full-charge process of AW32001A not only includes pre-charge, constant-current fast charge (CC) and constant voltage (CV) regulation, but also charge termination, auto-recharge, etc. The PPMF can manage the input source to power the system load and charge the battery simultaneously. The system load has a higher priority than the charge current. When the input power is limited by input current or voltage, the charge current will decrease automatically.

### **Main Machine**

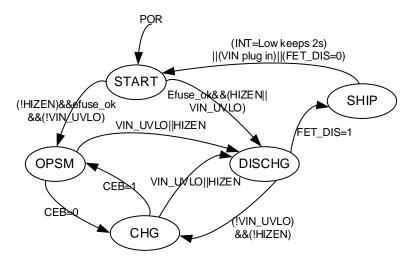

AW32001A includes: START, Battery Discharge Mode(DISCHG), Battery Charge Mode(CHG), Only Power System Mode(OPSM) and Shipping Mode(SHIP), Figure 11 is shown the main state machine conversion.

- (1) Battery Discharge Mode: Only Battery to SYS Path is enabled.

- (2) Battery Charge Mode: IN to SYS path and SYS to Battery path are enabled.

- (3) Only Power System Mode: Only IN to SYS Path is enabled.

- (4) Shipping Mode: All paths are disabled, AW32001A enters into low power consumption state.

Figure 11 The main state machine conversion

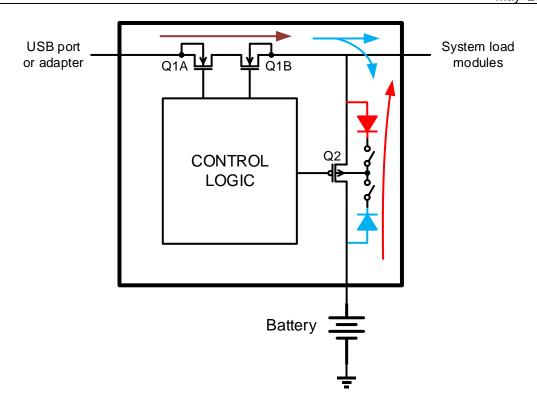

The AW32001A integrates an input reverse-block FET (Q1A), a LDO FET (Q1B) between IN and SYS, and a BATFET (Q2) between SYS and BAT. When VBUS plugs in and CEB=1, the device works in OPSM mode that only IN and SYS path is enabled, the system is powered by VBUS. If CEB=0, the charge function is enabled and Q2 turn on, the status switches to Battery Charge mode(CHG). When the system load demand is over the input power capacity, the PPMF of AW32001A will reduce the charging current or use power from the battery to satisfy the system load. The charge current is limited to maintain the system power supply with higher priority all the time. Figure 12 shows the PPMF structure of the AW32001A, which is called Battery Supplement Mode too. Once the VBUS is unplugged, the BATFET Q2 is turn on fully to supply the system, and the charger enters into Battery Discharge Mode(DISCHG). Further, the device can turn off BATFET so that the system voltage is zero to minimize the battery leakage current. When the host set FET\_DIS=1, the charger can turn off BATFET Q2 and entries Shipping Mode(SHIP).

Figure 12 Power Path management Structure

In Battery Charge Mode, the Q2 works as a fully featured linear charger with pre-charge, fast charge, constant voltage charge, charge termination, auto-recharge, thermal protection, built-in timer control and NTC monitoring. The charge current can be programmed via the I<sup>2</sup>C interface. When the chip's temperature exceeds the thermal regulation threshold (120°C default), the IC controls the charge current to reduce its temperature.

### **Power Supply**

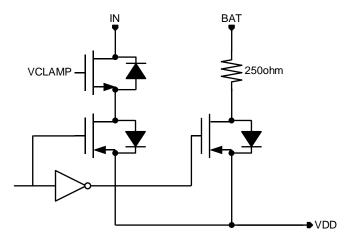

The AW32001A chooses the higher voltage of either BAT or IN to power VDD and the internal bias circuit, showed as Figure 13. When BAT or IN voltage rises above its respective power on reset (POR) threshold, the internal control circuit will wake up and the I<sup>2</sup>C interface will be ready for communication with all of registers reset to default value. These registers can be controlled by the host.

Figure 13 The inner power supply sources selection circuit for VDD

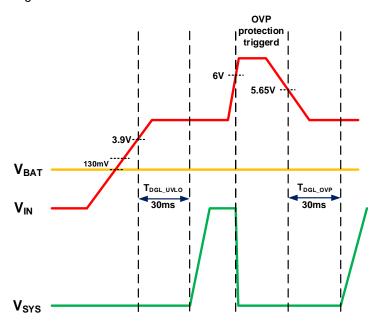

### VIN OVP, VIN UVLO and VIN GOOD

The AW32001A has an input UVLO and over-voltage protection (OVP) threshold. The Q1 is turned off immediately when the input voltage is out of its operating range.

The input over-voltage protection is integrated to prevent the device and other components from damage of the high input voltage (Voltage from VIN to GND). If the voltage at  $V_{IN}$  pin exceeds  $V_{IN\_OVP}$  threshold(6V typical), the chip will turn off Q1. When  $V_{IN}$  drops lower than the input overvoltage exit threshold (5.65V typical) and continues to exceed  $T_{DGL}$  OVP(30ms typical), Q1 will be turned on again.

When  $V_{IN}$  falls below  $V_{UVLO}$ , the Q1 is also turned off and the input to system loop controller is shut down. Once  $V_{IN}$  rises above  $V_{UVLO}+300$ mV and continues to exceed  $T_{DGL\_UVLO}(30$ ms typical), the Q1 is turned on and relative circuits start working.

Figure 14 Input Power Detection Operation

Either  $V_{IN}$  OVP or  $V_{IN}$  UVLO had happened, the device send out a 256µs low-state interrupt pulse from INT port, indicated a power fail status as REG08H[1]=0 and a fault status as REG09H[5]=1, which are read clear.

The VIN GOOD status not only means that VIN is between  $V_{IN\_UVLO}$  and  $V_{IN\_UVP}$ , but also .includes that the VIN voltage increase is higher than VBAT+170mV(130mV typical), and higher than VSYS+75mV(50mV typical). The all conditions have satisfied, and enter VIN GOOD. VIN voltage reduction meets VIN<VBAT+60mV or VIN<VSYS-50mV, exiting VIN GOOD.

### **Only Power System Mode**

The device meets VIN GOOD, EN\_HIZ=0(REG01H[4]=0) and CEB=1(REG01H[3]=1), and firstly enter Only Power System Mode(OPSM) which just turns on Q1A and Q1B, and supplies power the down-stream system by VBUS. If the device is configured CEB=0(REG01H[3]=0), the main state machine switches to Charge Mode from the Only Power System Mode.

### **Charge Mode**

When AW32001A operation in Charge Mode, the DPM, PPMF, Battery Supplement and other functions are available. These functions are useful in some application.

### **Battery Regulation Voltage**

The battery voltage of constant voltage regulation state is  $V_{BAT\_REG}$ . When  $V_{BAT\_REG} = 4.2V$ , the accuracy is  $\pm 0.5\%$  in the range of 0°C to +50°C ambient temperature.

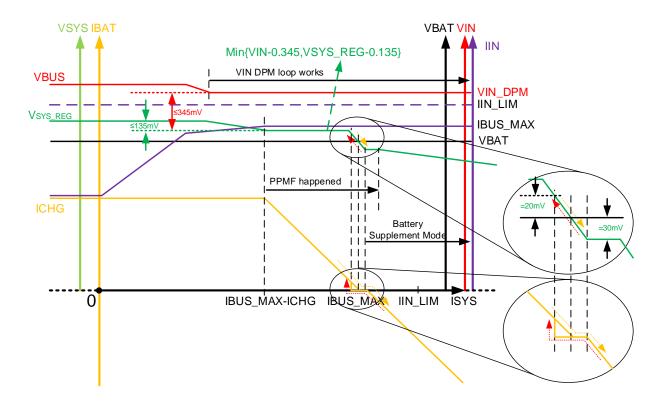

### Input Current-and Input Voltage-Based Power Regulation

The AW32001A has an input current limit regulation to meet the input source's (typically USB) maximum current limit specification. The function is realized by monitoring the input current continuously. If the rating of input source is lower than the preset input current limit, the input current limitation works to protect the input source from being overloaded. The total input current limit value can be set by the register IIN\_LIM (REG00H[3:0]), and the function can prevent the input source from being over-loaded.

Otherwise, when the load is over the input power capacity, the input voltage also can be regulated to  $V_{IN\_DPM}$  for the input voltage-based DPM regulation.  $V_{IN\_DPM}$  can be set via the register VIN\_DPM (REG00H[7:4]), and the  $V_{IN\_DPM}$  should be at least 250mV higher than  $V_{BAT\_REG}$  to ensure the stable operation of the regulator. The register DIS\_VINLOOP=1 (REG07H[6]=1) can be set to disable the input voltage limit function.

Either the input voltage or input current limit is reached, the total input power is limited by regulating the Q1B FET between IN and SYS. As a result, the system voltage drops. When the system voltage decrease to a **minimum value** of  $V_{SYS\_REG}$  - 135mV and  $V_{IN}$  - 345mV, the charge current is reduced to prevent the system voltage from dropping further.

### Power Path Management Function (PPMF)

The AW32001A can decouple the system from the battery by employs a PPMF with the Q2, which allows the device to control Q2 between the system and the battery separately. The system has high priority to start up by regulating the integrated Q1B even the battery is in a deeply discharged or missing state. The function of Q1A, Q1B and Q2 can be controlled by the I<sup>2</sup>C as shown in table 1.

| FET On/Off                 | HI-Z Mode and Charge Control |             |  |  |  |

|----------------------------|------------------------------|-------------|--|--|--|

| Changed by Control         | Set EN_HIZ = 1               | Set CEB = 1 |  |  |  |

| Q1A and Q1B                | OFF                          | х           |  |  |  |

| Q2(Charge Mode)            | х                            | OFF         |  |  |  |

| Q2(Battery Discharge Mode) | х                            | х           |  |  |  |

Table 1: FET Control via I2C

### NOTE: x=Don't care.

For the system voltage control, when the input voltage is lower than  $V_{SYS\_REG}$ , the Q1A and Q1B are fully on with the input current limit. When the input voltage is higher than  $V_{SYS\_REG}$ , the system voltage is regulated to  $V_{SYS\_REG}$ . The  $V_{SYS\_REG}$  can be programmed through REG07H[3:0].

### **Battery Supplement Mode**

When DPM occurs, the charge current is reduced to keep the input current or input voltage in regulation. If the charge current has already reduced to zero and the input source is still overloaded, the system voltage begins decreasing. If the system voltage drops to 30mV below the battery voltage, the AW32001A will enters battery supplement mode, and the ideal diode is enabled. If  $I_{DSCHG}$  (supplement current) \*  $R_{ON\_BATT}$  is lower than 30mV, the Q2 is regulated to keep  $V_{BAT}$  -  $V_{SYS}$  at 30mV. If this regulation cannot maintain 30mV voltage drop due to heavy load from SYS, the Q2 will fully turn on to maintain the ideal forward voltage. When the system load decreases, the system voltage starts to increase. The ideal diode mode is disabled, when  $V_{SYS}$  is higher than  $V_{BAT}$  + 20mV. Figure 15 shows the DPM and battery supplement mode operation profile.

When  $V_{\text{IN}}$  is not available, the AW32001A operates in discharge mode. During in discharge mode, the Q2 is fully on to reduce power loss.

Figure 15 DPM and Battery Supplement Operation Profile (Bad adaptor inserted)

**NOTE:** IBUS\_MAX is the maximum output current of the input source.

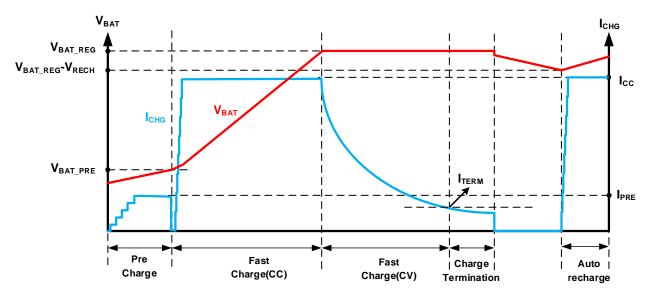

### **Battery Charge Profile**

The AW32001A has three main charging processes: pre-charge, fast constant current charge(CC), and fast constant voltage charge(CV):

Figure 16 Battery Charge Profile

- Pre-charge: In the pre-charge process, the IC charges the deeply depleted battery safely with small

current until the battery voltage rise to the pre-charge threshold (VBAT\_PRE), and then the chip enters the

fast-charge process. If the VBAT is not increasing to exceed than VBAT\_PRE before the pre-charge timer

expires (1 hour), the charge cycle stops, and a corresponding timeout fault signal is asserted. The register

REG03H[3:0] can be set the current of pre-charge.

- Fast constant current charge: When V<sub>BAT</sub> exceeds V<sub>BAT\_PRE</sub>, the AW32001A enters the fast constant charge process. The REG02H[5:0] can be set to change the fast-charge current.

- Fast constant voltage charge: The charge mode changes from CC mode to CV mode when the V<sub>BAT</sub> rises

to the battery-full voltage (V<sub>BAT\_REG</sub>) set via REG04H[7:2]. At the same time, the charge current starts

decreasing in CV charge process.

Due to multiple loop regulations, such as dynamic power management (DPM) regulation (input voltage, input current) or thermal regulation, the actual charge current may be less than the setting value.

When the charge current is smaller than termination current threshold I<sub>TERM</sub> for 3.2s in CV process, the charge cycle will be completed, and the charge status is updated to charge done. The register REG03H[3:0] can set the termination charge current threshold I<sub>TERM</sub>. The termination function can be disabled via EN\_TERM=0 (REG05H[4]=0). Meanwhile, the register bit TERM\_TMR (REG05H[0]) is able to control whether the charge process continue or not when the termination conditions are met. The termination function is shown as table 2.

| EN TERM       | TERM TMR         | After Termination Condition is Met |               |  |  |

|---------------|------------------|------------------------------------|---------------|--|--|

| LIN_ I LIXIVI | I LIXIVI_I IVIIX | Operation                          | Charge Status |  |  |

| 0             | Х                | Keep CV Charge                     | Charge        |  |  |

| 1             | 0                | Charge done                        | Charge done   |  |  |

| 1             | 1                | Keep CV Charge                     | Charge        |  |  |

Table 2: Termination Function Selection Table

### Note: x=Don't care.

A new charge cycle starts when any of the following conditions are valid:

- Auto-recharge kicks in.

- Battery charging is enabled via the I<sup>2</sup>C.

- The input power is recycled.

Under the following conditions:

- No safety timer fault.

- No thermistor fault at NTC.

- BFET is not forced off.

- No battery over-voltage event.

### Automatic Recharge

After the charge process is completed and charge cycle is terminated, the system's consumption or battery self-discharge may cause the battery voltage to decrease. When the battery voltage falls below the recharge threshold and  $V_{\text{IN}}$  is still in the operating range, another new charging cycle will start automatically. The recharge threshold(below  $V_{\text{BAT\_REG}}$ )  $V_{\text{RECH}}$  can be configured to 100mV or 200mV(default) via REG04H[0].

### **Battery Discharge Mode**

In Battery discharge mode, The device has low quiescent current and low on-resistance of Q2 to help the battery working for a longer time. Once the discharge current exceeds the over discharge current threshold, the over discharge current protection works and ensures the IC work safely in different applications.

### **Battery Discharge Function**

When the input source is absent and battery is connected to chip with the VBAT above  $V_{BAT\_UVLO}$  threshold, the Q2 is fully on. During discharge mode, the  $90m\Omega$  Q2 can minimizes conduction loss.

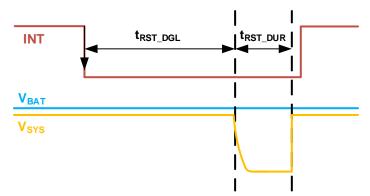

### **Battery Disconnection Function**

In some applications where the battery is not removable, it is essential to allow the system power to be reset in some applications or disconnect the battery from the system for shipping mode. The AW32001A provides both system reset function and shipping mode for different applications.

The INT pin can be used to cut off the path from the battery to the system under certain condition to reset the system manually. The battery is disconnected from the system, when the logic of INT is set low for longer than trender can be programmed by REG01H[7:6]). After a delay time of trender can be programmed by turned on automatically, and the system is powered by the battery again. The trender can be programmed by REG01H[5]. During the off period, the INT pin is not limited to be high or low. Please notes that the trender counter is triggered by the falling edge of INT.

Figure 17 System Reset Function Operation Timing Diagram

### **Shipping Mode**

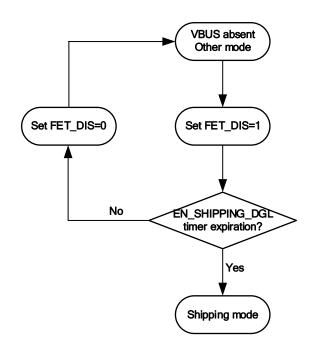

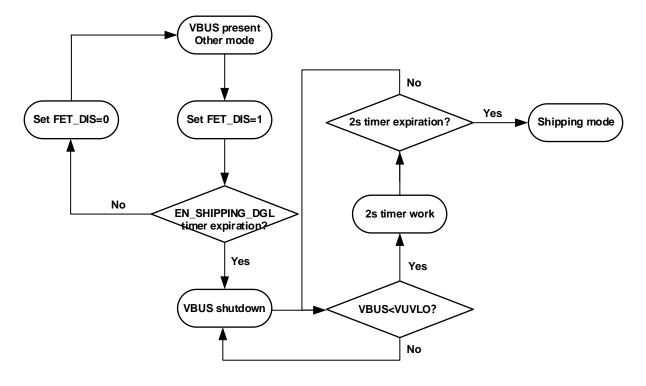

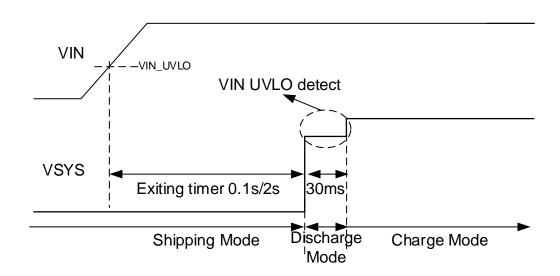

The register bit FET\_DIS (REG06H[5]) can be used to control the battery disconnection too. If the input source is absent, once setting FET\_DIS=1, the AW32001A enters shipping mode after a delay time (default 1s). The delay time can be programmed by EN\_SHIPPING\_DGL(REG09H[7:6]). If the input source is present when FET\_DIS is written to 1, chip will turn to shipping mode after 2s deglitch time with input voltage smaller than VIN\_UVLO threshold. Plug in the input adapter or pull the INT pin down for 2s or 100ms to wake the AW32001A up from shipping mode. The waking time can be configured in EN\_SHIPMD\_0P1S (REG0BH[0]) and INT100MS (REG22H[3]).

If INT PIN is shorted to ground or left floating before entering Shipping Mode, DIS\_SHIPINT (REG0CH[2]) must be written to 1 to avoid bad Shipping Mode operation. In this case, the only method of exiting shipping mode is plugging in the input adapter.

| FET On/Off         | Enter Shipping Mode | Exit Shipping Mode |              |  |

|--------------------|---------------------|--------------------|--------------|--|

| Changed by Control | Set FET_DIS to 1    | INT H to L for 2s  | Vin Plug-In  |  |

| Q1                 | х                   | х                  | On           |  |

| Q2                 | Off(1s later)       | On                 | On(2s later) |  |

Note: x=Don't care.

Figure 18 Enter Shipping Mode Timing Diagram(VBUS absent)

Figure 19 Enter Shipping Mode Timing Diagram(VBUS present)

Figure 20 Exit Shipping Mode Timing Diagram

Figure 21 Recovery charging From Shipping Mode Operation Timing Diagram(VBUS Plug-In)

# **Protection Operation**

The AW32001A has input OVP, UVLO, battery OVP and other functions to protect it's normal operation. Additionally, NTC function is integrated to prevent battery from high temperature danger. The following table 4 is all fault functions summary table.

Table 4: All fault functions summary table

| Status    | Operation Mode             | Brief Function Description                                                                                                                                                                                                                                     | Interrupt | Action                            |

|-----------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------|

| VIN GOOD  | Charge, OPSM               | V <sub>IN</sub> rises above V <sub>BAT</sub> +170mV and V <sub>SYS</sub> +75mV , the device enters into VIN Good, V <sub>IN</sub> falls down V <sub>BAT</sub> +60mV or V <sub>SYS</sub> -50mV, exits VIN GOOD. Entry and exit require 2ms to confirm.          | Yes       | Turn on Q1A and Q1B.              |

| VIN UVLO  | Charge, OPSM               | V <sub>IN</sub> falls down 3.3V, the deivce enters VIN UVLO immediately. V <sub>IN</sub> rises above 3.6V and keeps 30ms, the device exits.                                                                                                                    | Yes       | Turn off Q1A and Q1B.             |

| VIN OVP   | Charge, OPSM               | V <sub>IN</sub> rises above 6V, the device enters into VIN OVP immediately, V <sub>IN</sub> falls down about 5.65V, exits VIN OVP. Exit requires 30ms to confirm.                                                                                              | Yes       | Quickly turn off<br>Q1B in 100ns. |

| VBAT OVP  | Charge                     | After V <sub>BAT</sub> rises above V <sub>BAT_REG</sub> +130mV about 128µs, the device enters into VBAT OVP. Once V <sub>BAT</sub> falls down V <sub>BAT_REG</sub> +50mV about 2ms, exits VBAT OVP.                                                            | Yes       | Turn off Q2.                      |

| VBAT UVLO | Discharge, OPSM            | When V <sub>BAT</sub> rises above V <sub>BAT_UVLO+</sub> 190mV about 31ms (programmable 128µs), the device exits into V <sub>BAT_UVLO</sub> . Once V <sub>BAT</sub> falls down V <sub>BAT_UVLO</sub> (programmable), enters V <sub>BAT_UVLO</sub> immediately. | No        | Turn off Q2.                      |

| ОТР       | Charge, OPSM,<br>Discharge | When the junction temperature exceeds 150°C, IC shuts down. When the junction temperature falls below the thermal recovery temperature, approximately 130°C, the device restarts by using the soft-start sequence.                                             | Yes       | Turn off Q1B and Q2.              |

| PCB OTP   | Charge, OPSM,<br>Discharge | PCB_OTP function is default settings. V <sub>NTC</sub> falls down VDDx33%, PCB OTP is valid; Once V <sub>NTC</sub> rises up VDDx33%+70mV for 31ms, the device exits PCB OTP.                                                                                   | Yes       | Turn off Q1B and Q2.              |

| NTC HOT   | Charge                     | NTC HOT function is configured. V <sub>NTC</sub> falls down VDD×33%, the device judges battery hot, and reports NTC HOT; Once V <sub>NTC</sub> rises up VDD×33%+70mV for 31ms, the device exits NTC HOT.                                                       | Yes       | Turn off Q2.                      |

| NTC COOL  | Charge                     | NTC COOL function is configured. V <sub>NTC</sub> rises up VDD×64%, the device judges battery cool, and reports NTC COOL; Once V <sub>NTC</sub> falls down VDD×64%-60mV for 31ms, the device exits NTC COOL.                                                   | Yes       | Turn off Q2.                      |

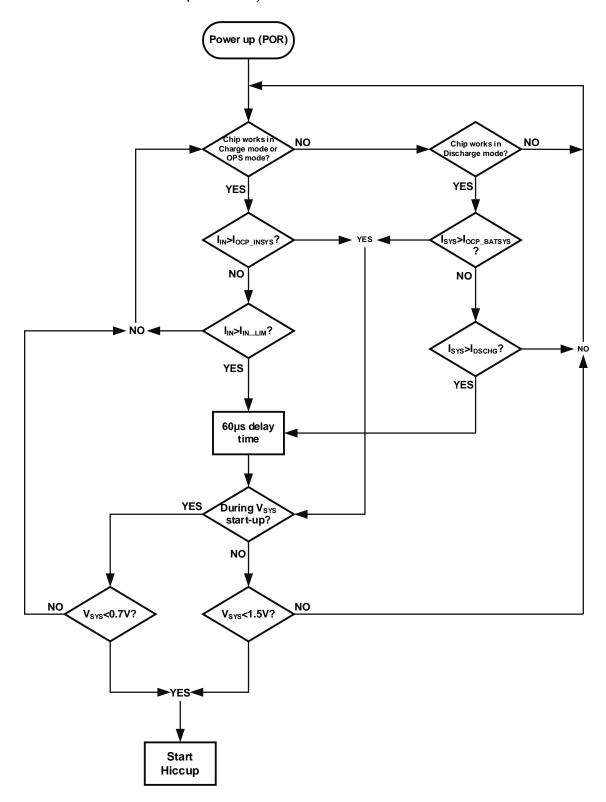

| VSYS SCP           | When the events including  Isys>Iocp_INSYS(2A),  Isys>Iocp_BATSYS(3.7A),  IIn_LIM <isys<iocp_insys 1ms="" 60us="" 60us,="" after="" again="" and="" device="" during="" for="" happen="" hiccup="" idschg<isys<iocp_batsys="" immediately="" in="" later.<="" launch="" mode.="" normally="" off="" or="" protection="" q1="" q2,="" short="" start="" th="" the="" triggers="" turn="" up="" vsys="" vsys<0.7v,="" vsys<1.5v,="" work="" working=""><th>Hiccup Mode.<br/>Turn off Q1 and<br/>Q2, and start up<br/>again after 1ms<br/>later</th></isys<iocp_insys> |                                                                                                                                                                                                                                                                                                                                                               |     | Hiccup Mode.<br>Turn off Q1 and<br>Q2, and start up<br>again after 1ms<br>later |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------|

| VBAT ODCP          | Discharge,<br>Supplement Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Over-discharge current protection. Once the I <sub>BAT</sub> exceeds the programmable discharge current limit I <sub>DSCHG</sub> (2A default) for 60µs. The AW32001A enters hiccup mode. In addition, if the discharge current goes high and reaches the internal fixed peak current limit (about 3.7A), the Q2 turns off and begins hiccup mode immediately. | No  | Q2 turns off                                                                    |

| Watch Dog<br>fault | Charge, OPSM,<br>Discharge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | When the watchdog timer expires, both the Q1 and Q2 are turned off, and most registers return to the default value, sent a watch dog fault interrupt to system.                                                                                                                                                                                               | Yes | Turn off Q1B<br>and Q2. Reset<br>CEB to 0.                                      |

| Safety time fault  | Pre Charge, Fast<br>Charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pre-charge for more than 1 hour (Configurable), or faster charge for more than 5 hours (Configurable), entry to safety time fault.                                                                                                                                                                                                                            | Yes | Turn off Q1B<br>and Q2. Reset<br>CEB to 0.                                      |

### Battery OVP(VBAT OVP)

The AW32001A has battery over-voltage protection (VBAT OVP) function (about 130mV higher than  $V_{BAT\_REG}$ ). When the battery OVP event occurs, AW32001A will stop the current charging cycle immediately and asserts a fault.

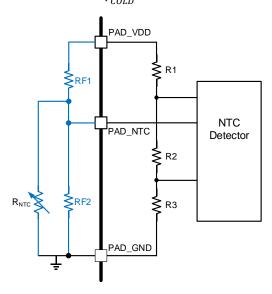

### Negative Temperature Coefficient (NTC) Temperature Sensor

The AW32001A is able to use NTC to sense the battery temperature. By monitoring the thermistor (usually available in the battery pack), the battery is guaranteed to operate in safe environment.

The NTC function demands appropriately valued resistors connecting from VDD to NTC to ground. At the same time, connect a thermistor from the NTC pin to ground. The NTC voltage is determined by the resistor divider and thermistor, and the divide ratio depends on the temperature of thermistor. The upper and lower bound of NTC voltage is pre-determined in AW32001A.

In the AW32001A, PCB\_OTP function is default settings. The  $I^2C$  can change the NTC and PCB\_OTP functions (see Table 5).

| I <sup>2</sup> C Contro | Function    |                       |

|-------------------------|-------------|-----------------------|

| EN_NTC                  | DIS_PCB_OTP | runction              |

| 0                       | x           | Disable               |

| 1                       | 1           | NTC(resistor-divided) |

| 1                       | 0           | PCB_OTP               |

Table 5: NTC Function Selection Table

### NOTE: x=Don't care

When PCB\_OTP is selected and the NTC voltage is lower than the NTC hot threshold, both the Q2 and Q1 are turned off. The NTC\_FAULT status is set (REG09H[1]) to 1 to show the PCB\_OTP fault. The IC Operation resumes, when the NTC voltage returns to safe range.

The NTC function works only in charge mode. Once the temperature is outside of the safe operating range, the IC stops charging state and report it on the status bits. When the temperature comes back to the safe range, the charge process resumes automatically.

### Thermal Regulation and Thermal Shutdown

The internal junction temperature is monitored continuously to avoid overheating the chip and maximize power delivery. When the internal junction temperature reaches the preset limit T<sub>J\_REG</sub> (120°C default), the charge current starts reducing to prevent dangerous high power dissipation. The IC can work in diffident thermal requirements applications, because it has multiple thermal regulation thresholds from 60°C to 120°C. register REG07H[5:4] can set The junction temperature regulation threshold.

The device has a built-in temperature sensor which monitors the internal junction temperature. When the junction temperature exceeds 150°C, the Q1 and Q2 will turn off. When the junction temperature falls below the thermal recovery temperature, approximately 130°C, the device reworks.

### System Short-Circuit Protection(VSYS SCP)

Figure 22 Short Circuit Hiccup Protection Flow Chart

The AW32001A has short-circuit protection (SCP) function in both the IN to SYS path and the BAT to SYS path. The IC monitor the system voltage continuously. If  $V_{SYS}$  is lower than 1.5V, The SCP is active, and  $I_{DSCHG}$  decreases to half of the original value. For the IN to SYS path, once  $I_{IN}$  is over the 2A protection threshold  $I_{OCP\_INSYS}$ , both the Q1 and Q2 are turned off immediately, and the AW32001A enters hiccup mode. When the

setting input current limit  $I_{\text{IN\_LIM}}$  is reached,  $I_{\text{IN}}$  is regulated at  $I_{\text{IN\_LIM}}$ . After a 60µs delay, the hiccup mode starts, and the hiccup mode interval is 1ms. For the BAT to SYS path, once  $I_{\text{BAT}}$  is over the 3.7A protection threshold  $I_{\text{OCP\_BATSYS}}$ , both the Q1 and Q2 are turned off immediately, and the AW32001A enters hiccup mode. When the battery discharge current limit threshold  $I_{\text{DSCHG}}$  is reached, hiccup mode starts after a 60µs delay, and the hiccup mode interval is 1ms.

Particularly, when system short-circuit occurs in both the input and battery, the both paths protection mechanism works together. The faster path dominates the hiccup operation.

### **Over-Discharge Current Protection**

In discharge mode and supplement mode, the AW32001A is designed to have an over-discharge current protection. Once the I<sub>BAT</sub> exceeds the programmable discharge current limit (2A default), the Q2 turns off after a 60µs delay. At the same time, the AW32001A enters hiccup mode as part of the over-current protection (OCP). The discharge current can be programmed to maximal 3.2A through the I<sup>2</sup>C. in addition, if the discharge current goes high and reaches the internal fixed peak current limit (about 3.7A), the Q2 turns off and begins hiccup mode immediately.

### Safety timer

Because the abnormal battery conditions, the AW32001A designed a pre-charge and fast-charge safety timer to prevent an extra-long time charging cycle. The pre-charge safety timer is 1hour, and the fast-charge safety timer can be programmed through the I<sup>2</sup>C. Once the battery enters fast-charge mode, The fast charge safety timer starts. The safety timer can be disabled via the I<sup>2</sup>C. When charger works in VIN DPM or Temp regulation state, the charge current will decrease. In order to charge as full as possible, the register bit TMR2X\_EN(REG06H[6]) could be set 1, which enable the timer slows down, the left safety time is double. If VIN DPM or Temp regulation state exit, or TMR2X\_EN=0, the timer recovery normal.

The following actions can restart the safety timer:

- Write REG05H[3] from 0 to 1 (safety timer enable).

- Write REG01H[3] from 1 to 0 (charge enable).

- Write REG02H[7] from 0 to 1 (software reset).

- A new charge cycle is kicked in.

### Interrupt to host (INT)

The AW32001A can output a 256µs low-state INT pulse via INT to notify the system of the operation. All of the below events can trigger an INT output:

- Charge completed

- Good input source detected

- Charging status change

- UVLO or input over-voltage protection

- Any fault in REG09H and REG08H (input fault, watchdog timer fault, safety timer fault, thermal fault, battery OVP fault, NTC fault)

When a fault occurs, an INT pulse is send out and latches the fault state in REG09H and REG08H. After the AW32001A exits the fault state, the fault bit is reset to 0 after the host reads faults registers. The NTC fault bit constantly reports the current thermistor conditions without latches. The INT signal can be masked when the corresponding control bit is set in REG06H[4:0]. When an INT condition is masked, this means that the INT pin signal (and register bit) will not trigger when the corresponding condition occurs. Masking INT pulses is useful when writing software code to avoid unnecessary interruptions due to these events.

### **Host Mode and Default Mode**

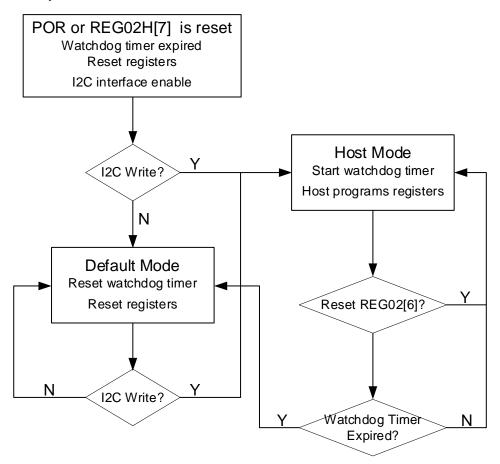

The AW32001A is a host-controlled device. After the power-on reset, the AW32001A starts up in a default mode or watchdog timer expiration state. All registers are in their default settings.

In both charge and discharge mode, once the watchdog timer run out, both the Q1 and Q2 are turned off, and most registers return to the default value (refer to the I<sup>2</sup>C Register Map section). The Q1 and Q2 are turn on again automatically after t<sub>RST\_DUR</sub>, which can be programmed by REG01H[5]. Also the watchdog timer can be turned off in discharge mode by setting REG05H[7]=0. If the watchdog timer (REG05H[6:5]) is not disabled, the host must reset the watchdog timer regularly by writing 1 to REG02H[6] before the watchdog timer expires to keep the device in host mode. When the watchdog timer expires, the AW32001A goes back to default mode. And any writing to the AW32001A will switch it to host mode. The watchdog timer limit can also be programmed or disabled by the host control.

In charge mode and OPSM, the watchdog timer is valid by default. In discharge mode, the watchdog timer is disable by default, and can be turned on by setting REG05H[7]=1. When the REG05H[6:5] is set to 00, the watchdog timer is disabled under both charge mode and discharge mode regardless of the status of REG05H[7]. Operation mode can be switched to default mode when one of the following conditions are valid:

- Register REG02H[7] is reset.

- Refresh input without battery.

- Re-insert battery with no VIN.

Figure 23 Watchdog Timer Flow Chart

### General I<sup>2</sup>C Operation

The device supports the I²C serial bus and data transmission protocol. It operates as a slave on the I²C bus. The maximum clock frequency specified by the I²C standard is 400kHz. Connect to the bus are made via the open-drain I/O pins SCL and SDA. The pull-up resistor can be selected in the range of  $1k\sim10k\Omega$  and the typical value is  $4.7k\Omega$  when I²C frequency is 400kHz. Different high level from 1.2V to 5V of this I²C interface is supported.

### **Device Address**

AW32001A 7-bit slave address (A7 $\sim$ A1) is 1001001 binary(0x49H). After the START condition, the I<sup>2</sup>C master sends the 7-bit chip address followed by an eighth (A0) read or write bit (R/W). R/W= 0 indicates a WRITE function and R/W = 1 indicates a READ function.

Table 6: Device Address

| Ī | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0  |

|---|----|----|----|----|----|----|----|-----|

|   | 1  | 0  | 0  | 1  | 0  | 0  | 1  | R/W |

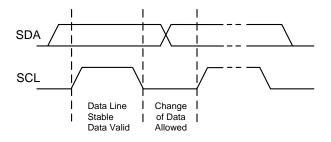

### Data Validation

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

Figure 24 Data Validation Diagram

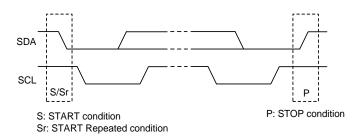

### PC Start/Stop

I<sup>2</sup>C start: SDA changes from high level to low level when SCL is high level.

I<sup>2</sup>C stop: SDA changes from low level to high level when SCL is high level.

Figure 25 Start and Stop Conditions

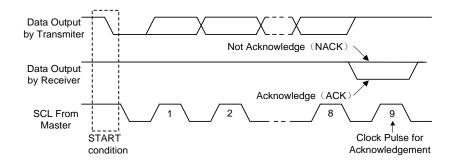

### ACK (Acknowledgement)

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends 8bits data, SDA must be released; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8bit data, releases the SDA and waits for ACK from master. If ACK is send and I<sup>2</sup>C stop is not send by master, slave device sends the next data. If ACK is not send by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

Figure 26 Acknowledgement Diagram

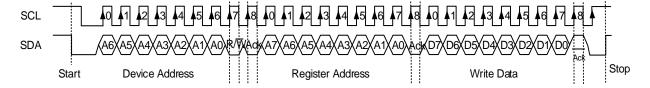

### Write Process

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- Master device generates START condition. The "START" signal is generated by lowering the SDA signal while the SCL signal is high.

- b) Master device sends slave address (7-bit) and the data direction bit (r/w = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master sends data byte to be written to the addressed register

- g) Slave sends acknowledge signal

- h) If master will send further data bytes the control register address will be incremented by one after acknowledge signal (repeat steps f and g)

- i) Master generates STOP condition to indicate write cycle end

Figure 27 I<sup>2</sup>C Write Timing

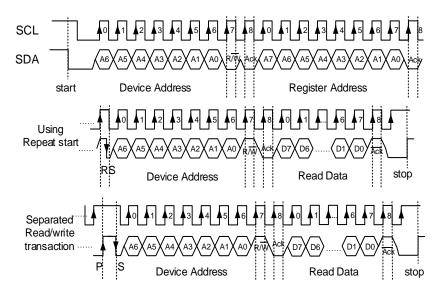

### Read Process

In a read cycle, the following steps should be followed:

- a) Master device generates START condition

- b) Master device sends slave address (7-bit) and the data direction bit (r/w = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master generates STOP condition followed with START condition or REPEAT START condition

- g) Master device sends slave address (7-bit) and the data direction bit (r/w = 1).

- h) Slave device sends acknowledge signal if the slave address is correct.

- i) Slave sends data byte from addressed register.

- j) If the master device sends acknowledge signal, the slave device will increase the control register address by one, then send the next data from the new addressed register.

- k) If the master device generates STOP condition, the read cycle is ended.

Figure 28 I<sup>2</sup>C Read Timing

# **Register List**

# Register Map

R/W = Read/Write, RC = Read Clear.

|         | rtodd, rriito, rto i | toda Olodii            |                        |                           |                |

|---------|----------------------|------------------------|------------------------|---------------------------|----------------|

| ADDR    | 0x00                 | 0x01                   | 0x02                   | 0x03                      | 0x04           |

| NAME    | Input Source Control | Power On Configuration | Charge Current Control | Discharge Current Control | Charge Voltage |

| Default | 0x8F                 | 0xAC                   | 0x0F                   | 0x91                      | 0XA3           |

| Bit7    |                      |                        | REG_RST                |                           |                |

| Bit6    | VIN_DPM[3:0]         | t <sub>RST_DGL</sub>   | WD_TMR_RST             | IDSCHG[3:0]               | VBAT_REG[5:0]  |

| Bit5    |                      | t <sub>RST_DUR</sub>   |                        | 1000110[0.0]              |                |