## SGM48523/SGM48524A SGM48525/SGM48526

## Dual 5A, High-Speed, Low-Side Gate Drivers with Negative Input Voltage Capability

## GENERAL DESCRIPTION

The SGM48523/4A/5/6 are dual high-speed low-side gate drivers for MOSFET and IGBT power switches. They have rail-to-rail driving capability and can sink and source up to 5A peak current with capacitive loads. The propagation delays are very short and well matched between the two channels that make the device very fit for applications that need accurate dual gate driving such as synchronous rectifiers. The matched propagation delays also allow for paralleling the two channels when higher driving current is required for example for paralleled switches. The input voltage thresholds are fixed, independent of supply voltage (V<sub>DD</sub>) and are compatible with low voltage TTL and CMOS logic. Noise immunity is excellent due to the wide hysteresis window between the input low and high thresholds. The devices have internal pull-up/pull-down resistors on the input pins to ensure low state on the driver outputs when the inputs are floating.

The SGM48523/4A/5 offer 3 logic options: dual inverting (SGM48523), dual non-inverting (SGM48524A), and one inverting and one non-inverting (SGM48525). They have independent enable pins (ENA and ENB) for each channel with active-high logic that can be left open for normal operation because of internal pull-up to VDD. The SGM48526 offers a flexible dual input design which can be configured as inverting (-INx) or non-inverting (+INx) for each channel. Both inputs (+INx or -INx) can control the output state. Typically, one input is used for gate pulse and the other one is used for enable/disable function.

The SGM48523/4A/5 are available in SOIC-8, MSOP-8 (Exposed Pad) and TDFN-3×3-8L packages. The SGM48526 is available in a Green TDFN-3×3-8L package. They operate over a temperature range of -40°C to +140°C.

## **FEATURES**

- Two Independent Gate Drive Channels

- 4.5V to 18V Single Supply Range (V<sub>DD</sub>)

- 5A Peak Source/Sink Pulse Current Drive

- Independent Enable Pin for Each Channel

- TTL and CMOS Compatible Logic Threshold

- Logic Levels Independent of Supply Voltage

- Hysteretic Input Logic for High Noise Immunity

- Outside and I amin I amend an Investor and Florida

- Outputs are Logic Low when Inputs are Floating

- Negative Voltage Handling Capability:

- -8V DC at Inputs

- -2V, 200ns Pulse for Outputs (OUTx)

- Glitch-Free Operation at Power-Up and Power-Down: Outputs Pulled Low during Supply UVLO

- Fast Propagation Delays: 18ns (TYP)

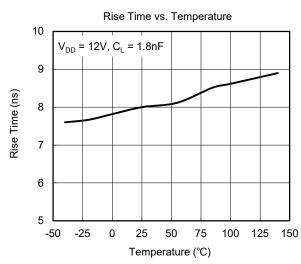

- Fast Rise Time: 8ns (TYP)

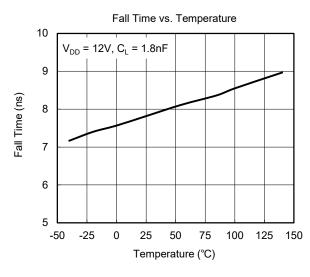

- Fast Fall Time: 8ns (TYP)

- Delay Matching between Two Channels: 1ns (TYP)

- Channels can be Paralleled for Higher Drive Current

- -40°C to +140°C Operating Temperature Range

- Packaging:

- SGM48523/4A/5 Available in Green SOIC-8, MSOP-8 (Exposed Pad) and TDFN-3×3-8L Packages

- SGM48526 Available in a Green TDFN-3×3-8L Package

#### **APPLICATIONS**

Power MOSFETs

IGBT Driving for Power Supplies

DC/DC Converters

Solar Power, Motor Drivers

Gate Drive for Emerging Wide Bandgap Devices

## PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION  | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING         | PACKING<br>OPTION   |

|-----------|-------------------------|-----------------------------------|--------------------|----------------------------|---------------------|

|           | SOIC-8                  | -40°C to +140°C                   | SGM48523XS8G/TR    | SGM<br>48523XS8<br>XXXXX   | Tape and Reel, 4000 |

| SGM48523  | MSOP-8<br>(Exposed Pad) | -40°C to +140°C                   | SGM48523XPMS8G/TR  | SGM48523<br>XPMS8<br>XXXXX | Tape and Reel, 4000 |

|           | TDFN-3×3-8L             | -40°C to +140°C                   | SGM48523XTDB8G/TR  | SGM<br>48523DB<br>XXXXX    | Tape and Reel, 4000 |

|           | SOIC-8                  | -40°C to +140°C                   | SGM48524AXS8G/TR   | SGM<br>CM9XS8<br>XXXXX     | Tape and Reel, 4000 |

| SGM48524A | MSOP-8<br>(Exposed Pad) | -40°C to +140°C                   | SGM48524AXPMS8G/TR | SGMR67<br>XPMS8<br>XXXXX   | Tape and Reel, 4000 |

|           | TDFN-3×3-8L             | -40°C to +140°C                   | SGM48524AXTDB8G/TR | SGM<br>R66DB<br>XXXXX      | Tape and Reel, 4000 |

|           | SOIC-8                  | -40°C to +140°C                   | SGM48525XS8G/TR    | SGM<br>48525XS8<br>XXXXX   | Tape and Reel, 4000 |

| SGM48525  | MSOP-8<br>(Exposed Pad) | -40°C to +140°C                   | SGM48525XPMS8G/TR  | SGM48525<br>XPMS8<br>XXXXX | Tape and Reel, 4000 |

|           | TDFN-3×3-8L             | -40°C to +140°C                   | SGM48525XTDB8G/TR  | SGM<br>48525DB<br>XXXXX    | Tape and Reel, 4000 |

| SGM48526  | TDFN-3×3-8L             | -40°C to +140°C                   | SGM48526XTDB8G/TR  | SGM<br>48526DB<br>XXXXX    | Tape and Reel, 4000 |

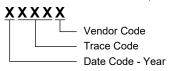

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

## SGM48523/SGM48524A SGM48525/SGM48526

## Dual 5A, High-Speed, Low-Side Gate Drivers with Negative Input Voltage Capability

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>DD</sub>     | 0.3V to 20V            |

|-------------------------------------|------------------------|

| INA, INB, ENA, ENB Voltage          | 8V to 20V              |

| OUTA, OUTB Voltage (DC)0.3          | V to $V_{DD}$ + 0.3V   |

| OUTA, OUTB Voltage (Pulse < 200ns)2 | $V$ to $V_{DD} + 0.3V$ |

| Package Thermal Resistance          |                        |

| SOIC-8, θ <sub>JA</sub>             | 121°C/W                |

| MSOP-8 (Exposed Pad), θJA           | 55°C/W                 |

| TDFN-3×3-8L, θ <sub>JA</sub>        | 70°C/W                 |

| Junction Temperature                | +150°C                 |

| Storage Temperature Range           | 65°C to +150°C         |

| Lead Temperature (Soldering, 10s)   | +260°C                 |

| ESD Susceptibility                  |                        |

| HBM                                 | 4000V                  |

| CDM                                 | 1000V                  |

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range                 | 4.5V to 18V     |

|--------------------------------------|-----------------|

| Input Voltage, INA, INB              | 2V to 18V       |

| Enable Voltage, ENA and ENB          | 2V to 18V       |

| Operating Junction Temperature Range | -40°C to +140°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

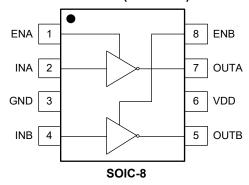

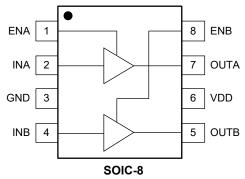

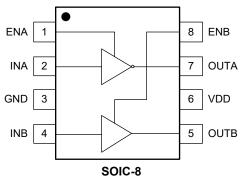

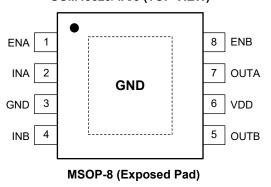

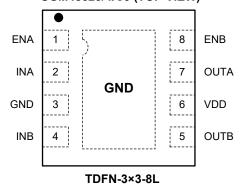

## PIN CONFIGURATIONS

## SGM48523 (TOP VIEW)

## SGM48524A (TOP VIEW)

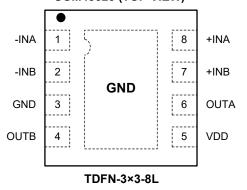

#### SGM48525 (TOP VIEW)

#### **SGM48523/4A/5 (TOP VIEW)**

## **SGM48523/4A/5 (TOP VIEW)**

#### SGM48526 (TOP VIEW)

## **PIN DESCRIPTIONS**

Table 1. Pin Functions of SGM48523, SGM48524A and SGM48525

| PIN         | NAME | I/O | FUNCTION                                                                                                                                                    |

|-------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | ENA  | ı   | Channel A Enable Input. Pull ENA high or leave it floating to enable OUTA output. Pull ENA low to disable OUTA output, ignoring INA state.                  |

| 2           | INA  | I   | Channel A Input. Inverting configuration in SGM48523/5 and non-inverting configuration in SGM48524A. OUTA is logic low if INA is unbiased or left floating. |

| 3           | GND  | _   | Ground. Reference pin for all signals.                                                                                                                      |

| 4           | INB  | I   | Channel B Input. Inverting configuration in SGM48523 and non-inverting configuration in SGM48524A/5. OUTB is logic low if INB is unbiased or left floating. |

| 5           | OUTB | 0   | Channel B Output.                                                                                                                                           |

| 6           | VDD  | I   | Power Supply Input.                                                                                                                                         |

| 7           | OUTA | 0   | Channel A Output.                                                                                                                                           |

| 8           | ENB  | 1   | Channel B Enable Input. Pull ENB high or leave it floating to enable OUTB output. Pull ENB low to disable OUTB output, ignoring INB state.                  |

| Exposed Pad | GND  | _   | Exposed Pad. It should be soldered to PCB board and connected to GND.                                                                                       |

#### Table 2. Pin Function of SGM48526

| PIN            | NAME | I/O | FUNCTION                                                                                                                                                                    |

|----------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | -INA | I   | Channel A Inverting Input. When +INA is used as a non-inverting input, pull -INA down to GND to enable OUTA output. OUTA is logic low if -INA is unbiased or left floating. |

| 2              | -INB | 1   | Channel B Inverting Input. When +INB is used as a non-inverting input, pull -INB down to GND to enable OUTB output. OUTB is logic low if -INB is unbiased or left floating. |

| 3              | GND  | _   | Ground. Reference pin for all signals.                                                                                                                                      |

| 4              | OUTB | 0   | Channel B Output.                                                                                                                                                           |

| 5              | VDD  | I   | Power Supply Input.                                                                                                                                                         |

| 6              | OUTA | 0   | Channel A Output.                                                                                                                                                           |

| 7              | +INB | I   | Channel B Non-Inverting Input. When -INB is used as an inverting input, pull +INB up to VDD to enable OUTB output. OUTB is logic low if +INB is unbiased or left floating.  |

| 8              | +INA | ı   | Channel A Non-Inverting Input. When -INA is used as an inverting input, pull +INA up to VDD to enable OUTA output. OUTA is logic low if +INA is unbiased or left floating.  |

| Exposed<br>Pad | GND  | _   | Exposed Pad. It should be soldered to PCB board and connected to GND.                                                                                                       |

NOTE: I: input, O: output.

## **FUNCTION TABLE**

Table 3. Device Logic Table (SGM48523, SGM48524A and SGM48525)

| SGM48523/4A/5 |          |          | SGM48523 |      | SGM48524A |      | SGM48525 |      |      |

|---------------|----------|----------|----------|------|-----------|------|----------|------|------|

| ENA           | ENB      | INA      | INB      | OUTA | OUTB      | OUTA | OUTB     | OUTA | OUTB |

| Н             | Н        | L        | L        | Н    | Н         | L    | L        | Н    | L    |

| Н             | Н        | L        | Н        | Н    | L         | L    | Н        | Н    | Н    |

| Н             | Н        | Н        | L        | L    | Н         | Н    | L        | L    | L    |

| Н             | Н        | Н        | Н        | L    | L         | Н    | Н        | L    | Н    |

| L             | L        | Any      | Any      | L    | L         | L    | L        | L    | L    |

| Any           | Any      | Floating | Floating | L    | L         | L    | L        | L    | L    |

| Floating      | Floating | L        | L        | Н    | Н         | L    | L        | Н    | L    |

| Floating      | Floating | L        | Н        | Н    | L         | L    | Н        | Н    | Н    |

| Floating      | Floating | Н        | L        | L    | Н         | Н    | L        | L    | L    |

| Floating      | Floating | Н        | Н        | L    | L         | Н    | Н        | L    | Н    |

Table 4. Device Logic Table (SGM48526)

| +INx (x = A or B) | -INx (x = A or B) | OUTx (x = A or B) |

|-------------------|-------------------|-------------------|

| L                 | L                 | L                 |

| L                 | Н                 | L                 |

| Н                 | L                 | Н                 |

| Н                 | Н                 | L                 |

| Floating          | Any               | L                 |

| Any               | Floating          | L                 |

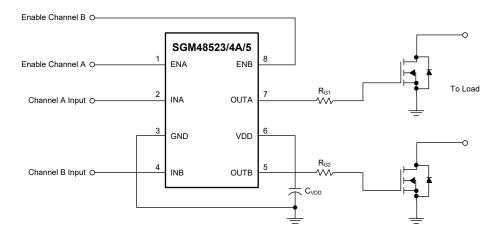

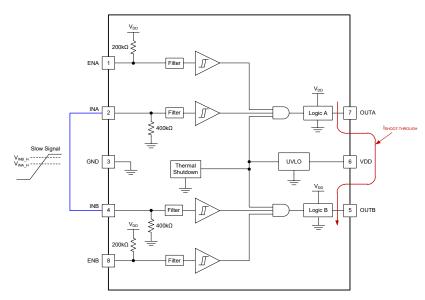

## TYPICAL APPLICATION CIRCUITS

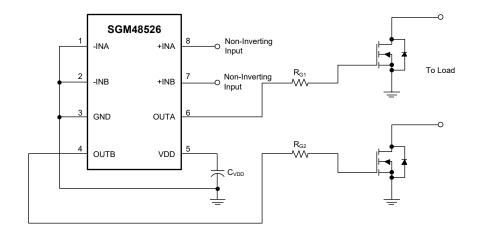

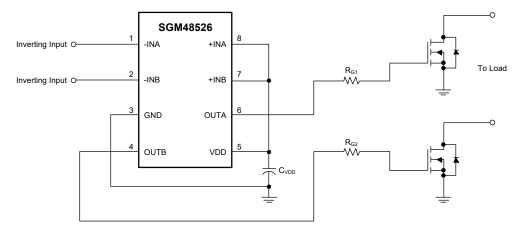

Figure 1. SGM48523/4A/5 Typical Application

Figure 2. SGM48526 with Channel A and Channel B in Non-Inverting Configuration

Figure 3. SGM48526 with Channel A and Channel B in Inverting Configuration

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 12V, C_{VDD} = 1\mu F, T_J = -40^{\circ}C$  to +140°C, typical values are at  $T_J = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                             | SYMBOL                 |                                                    | CONDITIONS                                       | MIN | TYP  | MAX   | UNITS |

|-------------------------------------------------------|------------------------|----------------------------------------------------|--------------------------------------------------|-----|------|-------|-------|

| Power Supplies                                        |                        | •                                                  |                                                  |     |      |       |       |

| VDD Supply Voltage                                    | $V_{DD}$               |                                                    |                                                  | 4.5 |      | 18    | V     |

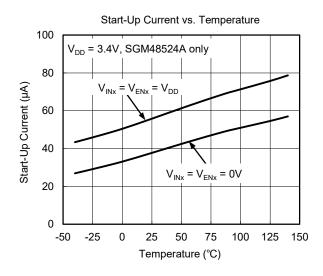

|                                                       |                        | 001440500                                          | $V_{DD} = 3.4V, V_{INA} = V_{INB} = 0V$          |     | 74   | 119   | -     |

|                                                       |                        | SGM48523                                           | $V_{DD} = 3.4V$ , $V_{INA} = V_{INB} = V_{DD}$   |     | 36   | 65    |       |

|                                                       |                        | 0014405044                                         | $V_{DD} = 3.4V, V_{INA} = V_{INB} = 0V$          |     | 38   | 70    |       |

| V/DD Otant Ha Oranget                                 |                        | SGM48524A                                          | $V_{DD} = 3.4V$ , $V_{INA} = V_{INB} = V_{DD}$   |     | 56   | 102   |       |

| VDD Start-Up Current                                  | I <sub>DD_OFF</sub>    | CCMARTOE                                           | $V_{DD} = 3.4V, V_{INA} = V_{INB} = 0V$          |     | 57   | 98    | μA    |

|                                                       |                        | SGM48525                                           | $V_{DD} = 3.4V$ , $V_{INA} = V_{INB} = V_{DD}$   |     | 49   | 82    |       |

|                                                       |                        | CCMARERO                                           | $V_{DD} = 3.4V, V_{+INA} = V_{+INB} = 0V$        |     | 38   | 70    |       |

|                                                       |                        | SGM48526                                           | $V_{DD} = 3.4V$ , $V_{+INA} = V_{+INB} = V_{DD}$ |     | 56   | 102   |       |

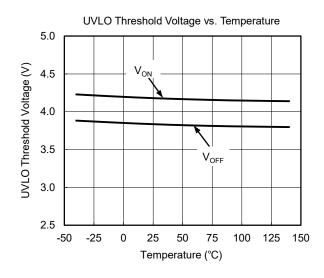

| Complete Otant Through ald                            | .,                     | TJ = +25°C                                         |                                                  | 3.8 | 4.2  | 4.5   | V     |

| Supply Start Threshold                                | V <sub>ON</sub>        | T <sub>J</sub> = -40°C to                          | +140°C                                           | 3.7 | 4.2  | 4.7   | V     |

| Minimum Operating VDD Voltage after Supply is Started | $V_{OFF}$              |                                                    |                                                  |     | 3.85 | 4.3   | V     |

| VDD Supply Voltage Hysteresis                         | V <sub>DD_HYS</sub>    |                                                    |                                                  | 0.2 | 0.35 | 0.5   | V     |

| Input Pins (INA, INB, +INA, -INA, +INB, -INB          | )                      |                                                    |                                                  |     |      |       |       |

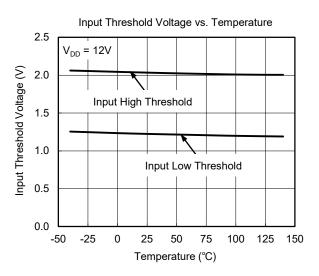

| Input Signal High Threshold                           | V <sub>IN_H</sub>      | Output low for                                     | r non-inverting input pins inverting input pins  | 1.8 | 2    | 2.2   | V     |

| Input Signal Low Threshold                            | $V_{IN\_L}$            |                                                    | non-inverting input pins r inverting input pins  | 1.0 | 1.2  | 1.4   | ٧     |

| Input Hysteresis                                      | V <sub>IN_HYS</sub>    |                                                    |                                                  | 0.6 | 0.8  | 1.0   | V     |

| Enable Pins (ENA, ENB)                                |                        |                                                    |                                                  |     |      |       |       |

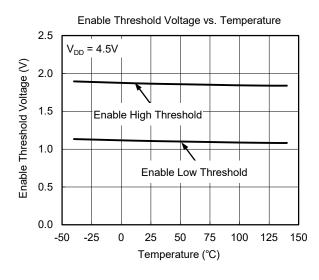

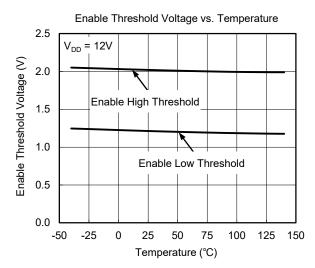

| Enable Signal High Threshold                          | V <sub>EN_H</sub>      | Output high fo                                     | r non-inverting input pins                       | 1.8 | 2    | 2.2   | V     |

| Enable Signal Low Threshold                           | V <sub>EN_L</sub>      | Output low for                                     | non-inverting input pins                         | 1.0 | 1.2  | 1.4   | V     |

| Enable Hysteresis                                     | V <sub>EN_HYS</sub>    |                                                    |                                                  | 0.6 | 0.8  | 1.0   | V     |

| Output Pins (OUTA, OUTB)                              |                        |                                                    |                                                  |     |      |       |       |

| High Level Output Voltage                             | V <sub>OH</sub>        | $V_{OH} = V_{DD} - V_{O}$                          | <sub>UT</sub> , I <sub>OUT</sub> = -10mA         |     |      | 0.061 | V     |

| Low Level Output Voltage                              | V <sub>OL</sub>        | I <sub>OUT</sub> = 10mA                            |                                                  |     |      | 0.009 | V     |

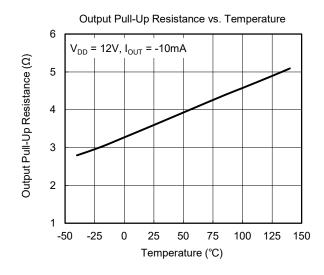

| Output Pull-Up Resistance (1)                         | R <sub>OH</sub>        | I <sub>OUT</sub> = -10mA                           |                                                  |     | 4    | 6.1   | Ω     |

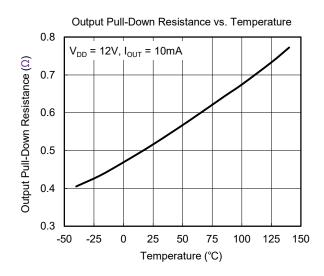

| Output Pull-Down Resistance                           | R <sub>OL</sub>        | I <sub>OUT</sub> = 10mA                            |                                                  |     | 0.5  | 0.9   | Ω     |

| Real Output Current                                   | I <sub>PK_SOURCE</sub> | C = 0.22E f                                        | - 1111-                                          |     | 5    |       | Α     |

| Peak Output Current                                   | I <sub>PK_SINK</sub>   | $I_{PK\_SINK}$ $C_L = 0.22\mu F$ , $f_{SW} = 1kHz$ |                                                  |     | 5    |       | Α     |

| Protection Circuits                                   |                        |                                                    |                                                  |     |      |       |       |

| Thermal Shutdown Temperature                          | T <sub>TSD</sub>       |                                                    |                                                  |     | 165  |       | °C    |

| Thermal Shutdown Temperature Hysteresis               | T <sub>HYS</sub>       |                                                    |                                                  |     | 15   |       | °C    |

#### NOTE:

1.  $R_{\text{OH}}$  represents constant pull-up resistance only.

## **SWITCHING CHARACTERISTICS**

$(V_{DD} = 12V, C_{VDD} = 1\mu F, T_J = -40^{\circ}C$  to +140°C, typical values are at  $T_J = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                               | SYMBOL          | CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|---------------------------------------------------------|-----------------|--------------------------------------------------|-----|-----|-----|-------|

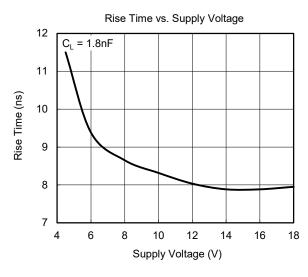

| Rise Time (1)                                           | t <sub>R</sub>  | C <sub>L</sub> = 1.8nF                           |     | 8   |     | ns    |

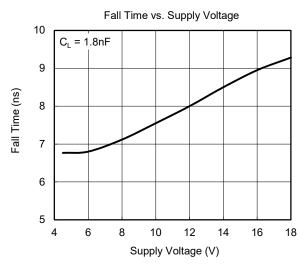

| Fall Time (1)                                           | t <sub>F</sub>  | C <sub>L</sub> = 1.8nF                           |     | 8   |     | ns    |

| Delay Matching between Two Channels                     | t <sub>M</sub>  | INA = INB, OUTA and OUTB at 50% transition point |     | 1   |     | ns    |

| Minimum Input Pulse Width that Changes the Output State | t <sub>PW</sub> |                                                  |     | 15  |     | ns    |

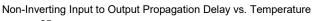

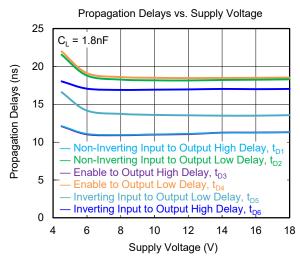

| Non-Inverting Input to Output Propagation Delay (1)     | t <sub>D1</sub> | C <sub>L</sub> = 1.8nF, 5V input pulse           |     | 11  |     | 200   |

| Non-inverting input to Output Propagation Delay         | t <sub>D2</sub> | C <sub>L</sub> = 1.8nF, 5V input pulse           |     | 18  |     | ns    |

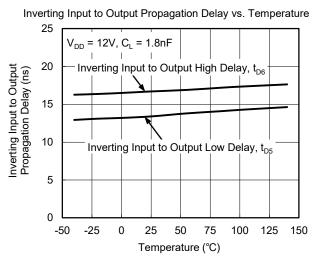

| Enable to Output Propagation Delay (1)                  | t <sub>D3</sub> | C <sub>L</sub> = 1.8nF, 5V enable pulse          |     | 11  |     | 20    |

| Enable to Output Propagation Delay                      | t <sub>D4</sub> | C <sub>L</sub> = 1.8nF, 5V enable pulse          |     | 18  |     | ns    |

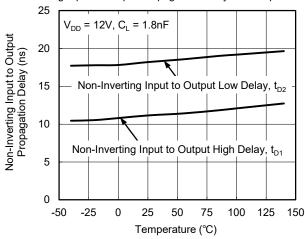

| Inverting Input to Output Propagation Delay (1)         | t <sub>D5</sub> | C <sub>L</sub> = 1.8nF, 5V input pulse           |     | 14  |     | 200   |

| Inverting input to Output Propagation Delay             | t <sub>D6</sub> | C <sub>L</sub> = 1.8nF, 5V input pulse           |     | 16  |     | ns    |

#### NOTE:

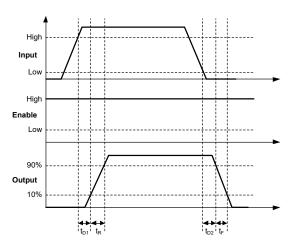

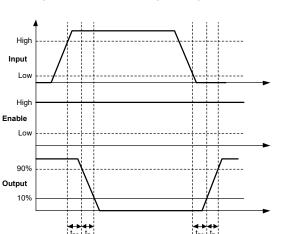

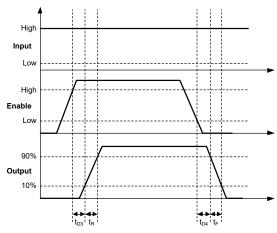

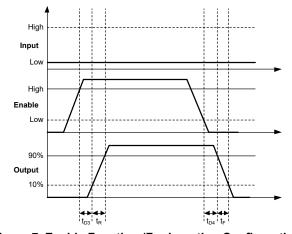

1. See timing diagrams as shown in Figure 4 through Figure 7.

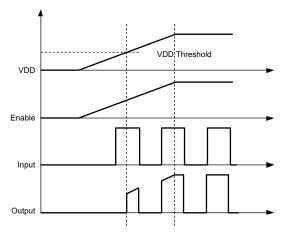

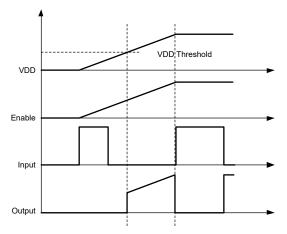

## **TIMING DIAGRAMS**

Figure 4. Non-Inverting Configuration

Figure 6. Inverting Configuration

Figure 5. Enable Function (For Non-Inverting Configuration)

Figure 7. Enable Function (For Inverting Configuration)

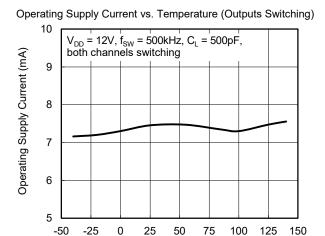

## TYPICAL PERFORMANCE CHARACTERISTICS

Temperature (°C)

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

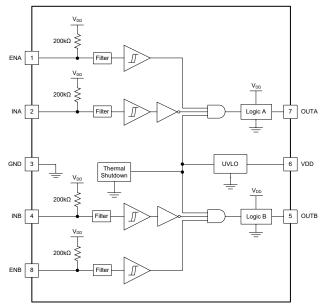

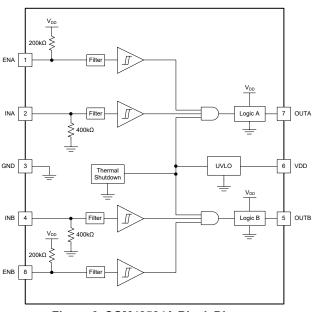

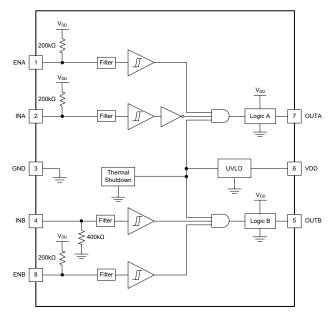

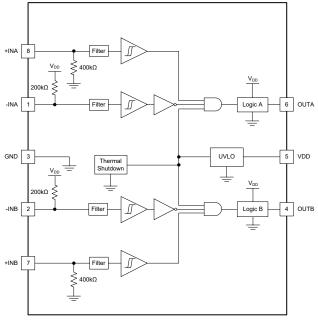

## **FUNCTIONAL BLOCK DIAGRAMS**

Figure 8. SGM48523 Block Diagram

Figure 9. SGM48524A Block Diagram

Figure 10. SGM48525 Block Diagram

Figure 11. SGM48526 Block Diagram

#### **DETAILED DESCRIPTION**

The SGM48523/4A/5/6 dual-channel, low-side, high-speed gate drivers are among the top level devices in the market featuring a 5A source/sink current capability and industry best-in-class switching characteristics.

They have several other prominent features as listed in Table 5 assuring that they are reliable and efficient gate driving solutions for power switches in high frequency applications.

**Table 5. Prominent Features and Benefits**

| Feature                                                                 | Benefit                                                                                                                                         |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Best-in-class propagation delays (18ns, TYP).                           | Very low delay and distortion in pulse transmission.                                                                                            |

| Excellent delay matching between channels (1ns, TYP).                   | Allows paralleling of the channel outputs for double current driving capability. It is especially useful for driving paralleled power switches. |

| Wide supply voltage range (V <sub>DD</sub> from 4.5V to 18V).           | Design Flexibility.                                                                                                                             |

| Wide operating temperature range (-40°C to +140°C).                     | Wider system operating temperature range and smaller cooling system.                                                                            |

| UVLO protection on VDD.                                                 | Driver outputs are logic low in UVLO condition to ensure controlled and glitch-free driving during power-up and power-down.                     |

| Outputs are logic low when inputs (INx) are floating.                   | This safety feature prevents unexpected gate pulses during abnormal situations such as the conditions tested in the safety certification.       |

| Outputs are enabled when enable inputs (ENx) are floating.              | This feature provides pin-to-pin compatibility with other similar products in those designs where pin 1 and 8 are floating.                     |

| Wide hysteresis CMOS/TTL compatible input and enable thresholds.        | Improved noise immunity while compatible with digital logic (3.3V, 5V).                                                                         |

| Input/enable pins voltage levels are not restricted by V <sub>DD.</sub> | Simplified system especially in the auxiliary bias supply architecture.                                                                         |

| Ability to handle -8V V <sub>DC</sub> (MAX) at input pins.              | Increased robustness in noisy environments.                                                                                                     |

#### **Under-Voltage Lockout for VDD**

The internal under-voltage lockout (UVLO) protection keeps the outputs in low state when the VDD supply voltage is insufficient for proper operation of the chip. If  $V_{\text{DD}}$  rises but its voltage does not reach UVLO threshold, the outputs are logic low, ignoring the state of the inputs. The UVLO rising threshold voltage is 4.2V (TYP) and has a 350mV (TYP) hysteresis band to prevent output from chattering when  $V_{\text{DD}}$  has large

superimposed noise or other fluctuations. The safe low voltage (less than 5V) operating capability along with the excellent switching characteristics makes the device well suited for driving GaN power switches.

If the enable pin is active or floating during power-up, the output remains low until  $V_{DD}$  exceeds the UVLO threshold. Then the output is controlled by the input signal with a magnitude that follows  $V_{DD}$  (see Figure 12 for non-inverting and Figure 13 for inverting channels).

Figure 12. Power-up in a Non-Inverting Driver Channel

Figure 13. Power-up in an Inverting Driver Channel

## **DETAILED DESCRIPTION (continued)**

Because VDD pin is the supply source for the device internal circuits, it is recommended to use two  $V_{\text{DD}}$  surface mount bypass capacitors to prevent noise problems caused by high speed switching. A small 100nF ceramic capacitor must be soldered as close between the VDD and GND pins as possible. In addition, a larger low ESR capacitor (a few  $\mu$ F) must be placed in parallel and close to the same pins for delivery of the high peak driving currents with sharp rise time. The low impedance characteristic provided by these capacitors allows high frequency and high current driving of the outputs. Avoid using vias for connecting bypass capacitors to the device pins.

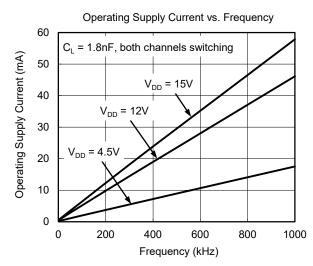

## **Operating Supply Current**

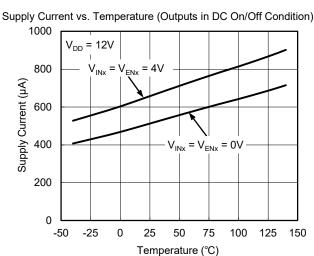

The SGM48523/4A/5/6 consume a very low guiescent current. The lowest quiescent IDD value is reached when the device is fully powered (not in UVLO), and the outputs are in a low or high DC static state and the internal pull-up inputs (enable inputs) are in high or float state. During normal operation, the total IDD current is the sum of three components: the quiescent current, the average IOUT current due to switching and the internal pull-up resistor currents (on enable inputs and inverting inputs). Clearly if an inverting input pin that has an internal pull-up resistor is externally pulled low, a small additional current is drawn from V<sub>DD</sub> through the internal pull-up resistor (see Figure 8 through Figure 11). Usually the main portion of the supply current is for driving the outputs and the other two can be ignored. For driving MOSFETs with a frequency of f<sub>SW</sub> and gate charge of Q<sub>g</sub>, the average driver output current is I<sub>OUT</sub> =  $Q_g \times f_{SW}$ .

#### **Input Stage**

The SGM48523/4A/5/6 input pins are compatible with TTL and CMOS logic thresholds and are independent of the supply voltage ( $V_{DD}$ ). The logic high threshold is typically around 2V and the low threshold is around 1.2V. Therefore the inputs can be easily driven by a 3.3V or 5V digital controller. The noise immunity is enhanced due to the relatively wide hysteresis band (2V - 1.2V = 0.8V, TYP) compared to the traditional TTL logic in which the hysteresis is typically less than 0.5V. The input voltage thresholds of the SGM48523/4A/5/6 are tightly controlled to simplify the system design and assure stable operation against wide temperature variations. Also the devices are designed with very low parasitic input pin capacitances to allow high speed switching.

An important safety feature of the drivers is that if any of the input pins floats, the corresponding channel output will be held in the low state. This feature is implemented by the GND pull-down resistors on the non-inverting inputs and VDD pull-up resistors on the inverting inputs as shown in Figure 8 through Figure 11.

The SGM48526 has two input pins in each channel to control the output. The SGM48526 offers the flexibility to use either a non-inverting input (+INx) or an inverting input (-INx) to drive the output on each channel. The output state depends on both +INx and -INx pins (x = Aor B). When one input pin is chosen to drive the output, the other unused input cannot be left floating and must be biased to allow output control by the other pin. As explained before if an input is floating, the channel output is disabled by the internal pull-up or pull-down resistors for safety. The unused input pin can function as enable/disable input. In summary, the SGM48526 output is only driven high when +INx pin is high and -INx is low. The details are provided in the function table and the application diagrams given in Figure 2 and Figure 3.

The input driving signal must have short rise or fall time. This condition is normally satisfied when the input signals are generated by a PWM controller or logic gate (with transition times < 200ns). If the input transition is too slow, the output may chatter several times (at high frequency) before going to its new stable state. The wide input hysteresis of these devices minimizes the concern for such problem even for other logic thresholds. However, the designer should make sure implementation satisfies the driver requirements. To limit the rise or fall time of the gate pulse on the output, it is recommended to use an external series resistance between the driver output and the gate of the power device. This resistor reduces the switching gate charge losses in the driver output stage because a portion of the loss will dissipate in the resistor.

#### **Enable**

The enable function is very useful in some applications that need to block gate pulses depending on the system operating conditions. For example, in a synchronous rectifier and in light load conditions, it may be necessary to disable gate signal to avoid negative current in the device for improving efficiency or to prevent boosting in a buck converter.

## **DETAILED DESCRIPTION (continued)**

The SGM48523/4A/5 devices have an independent active-high enable pin (ENx). Similar to the driver inputs, the enable pins are independent of the supply voltage with tightly controlled thresholds and are compatible with TTL or CMOS logic. They can be directly controlled by the popular 3.3V and 5V microcontrollers. The ENx pins (x = A or B) are internally pulled up to VDD by pull-up resistors and the output channel x is enabled if ENx input is floating. Therefore the SGM48523/4A/5 are pin-to-pin compatible with SGMICRO's previous gate driver. Note that if two channels in a device are paralleled, the enable signals should also be tied together.

The SGM48526 device does not have specified enable pins. However, the unused input pin can be used to enable or disable the device. Either pulling +INx down to GND or pulling -INx up to VDD disables the output. Therefore, +INx pin is used as an active high enable pin, while -INx is used as an active low enable pin. Note that while the ENA and ENB pins in SGM48523/4A/5 are allowed to be floating during normal operation and the outputs will be enabled. The unused input pins in SGM48526 are not allowed to be floating.

## Tightly Matched and Low Propagation Delays

The SGM48523/4A/5/6 drivers offer very low propagation delays (18ns, TYP), and pulse transmission distortion between input and output. Such low distortion is important in the industry for high frequency switching

applications, for example, in the synchronous rectifier applications where both SR MOSFETs are driven with one driver. Moreover, the delays between the two channels are extremely well matched with 1ns (TYP) difference. This feature is critically important when accurate timing between dual gate drives is required. For example, in some PFC applications, two paralleled MOSFETs may be needed to be driven independently using each output channel and with the same input pulses. The matching gate drivers ensure that they are driven simultaneously with the minimum turn-on or turn-off delay differences. The tight matching also allows for paralleling the two channels to increase current driving capability. The INA and INB pins are tied together as input and OUTA and OUTB pins are tied together as output. Caution must be exercised that any delay between triggering of the two channels can lead to a shoot-through between outputs. Note that as described in Figure 14, the input signals must also be well matched and with fast rise or fall time. Due to the small differences between the input thresholds, a pulse with slow rise or fall time may add extra delay between signals. Therefore, it is recommended to use very fast input pulses (20V/µs or greater) when inputs are paralleled. Also, the tie point for inputs must be as close as possible to the chip. If possible, adding external series gate resistors between the outputs will also help. Considering small  $0\Omega$  series output resistors in the layout is recommended to allow future adjustment in the design if needed.

Figure 14. When channels are paralleled for higher drive current, slow rise or fall time of the input pulse can cause shoot-through between device outputs. Inputs with dv/dt higher than 20V/µs are recommended

## **APPLICATION INFORMATION**

In order to achieve fast switching and to reduce losses in the power switches, high current gate drivers with sufficient drive voltage are required. Such function cannot be directly provided by logic controllers usually operating at low power and low voltages such as 3.3V. Even traditional buffer drivers like totem-pole NPN/PNP configurations, are not useful as they are not capable for voltage level shifting. A gate driver device provides other advantages in the system such as reduction of the high frequency noise by placing the high current driver close to the power switch, and reduction of power dissipation and thermal stress in controllers because gate-charge power losses are handled by the driver. Moreover, with the emerging of wide band-gap power devices such as GaN based switches that are capable for operating at very high frequency, new gate driving requirements are imposed on the driver devices. Such requirements include operating at low supply voltages (5V or less), low propagation delays and excellent delay matching, and compact layout with low inductance and enhanced thermal capability.

In summary, gate driver devices simplify the system design and provide better performance, lower cost, lower component count and require less space on the board.

#### Supply Voltage V<sub>DD</sub>

The supply voltage is selected based on the power switch and driving requirements. Some power switches, need positive gate voltage for turn-on and negative for turn-off and for some other types, it is reversed. In both cases the differential drive voltage is equal to  $V_{DD}$  that can be selected in a wide range from 4.5V to 18V. This gate driver can be used for driving of a variety of power switches. Typically for Si MOSFETs, the driving  $V_{GS}$  is chosen to be 4.5V, 10V or 12V depending on the application and switch class. For IGBTs, a  $V_{GE}$  of 15V or 18V is commonly used.

#### **Propagation Delay**

The propagation delays depend on the operating switching frequency and the permissible pulse distortion. All devices present very short 18ns (TYP) propagation delays. Switching characteristics with more details are provided to illustrate the propagation and switching performance.

### **Drive Current and Power Dissipation**

MOSFETs are widely used as power switches in many high frequency applications. The SGM48523/4A/5/6 can source and sink 5A at 12V for a pulse width of several hundred nanoseconds for driving MOSFETs. High peak driving current is usually needed for a quick turn on and usually the same amount of current in opposite direction is also needed for switch turn off. The sourcing and sinking actions repeat at the switching frequency and for each transition some energy is dissipated in the driver device.

The amount of power dissipation in the device depends on the following:

- · Switching frequency.

- Gate charge required to turn the MOSFET on or off.

- Size of the external gate resistors used (if any).

Gate charge is usually a function of the  $V_{GS}$  drive voltage. The drive voltage is  $V_{GS} \approx V_{DD}$  (the dropout of the driver,  $V_{OH}$ , is normally very low). Note that due to the low quiescent current and the internal bias power, the loss in the driver is effectively equal to the output driving losses caused by drive currents.

Using a discrete capacitor  $(C_g)$  as a similar switch gate load for testing, the loss in the driver can be easily estimated. The energy that is needed to charge the capacitor to the supply voltage  $V_{DD}$  is given by (1):

$$E_{G} = \frac{1}{2}C_{g}V_{DD}^{2} \tag{1}$$

It can be proved that the same amount of energy is dissipated in the driver output stage resistances. Also, the same amount of energy is dissipated if the capacitor is discharged by the driver. Therefore, with a switching frequency of  $f_{\text{SW}}$ , the total power loss (in one channel) is:

$$P_{G} = C_{g}V_{DD}^{2}f_{SW}$$

(2)

As an example, with  $V_{DD}$  = 12V,  $C_g$  = 10nF and  $f_{SW}$  = 200kHz the driver loss is calculated as:

$$P_{G} = 10nF \times 12V \times 12V \times 200kHz = 288mW$$

(3)

## **APPLICATION INFORMATION (continued)**

The test is implemented on MOSFETs to find the equivalent gate capacitance to determine the gate charge required for switching the device. The gate charge includes the impact of the input gate-source and drain-gate capacitances. The drain-gate capacitance also needs current for charge and discharge due to the voltage swing of the drain voltage when the power device is turning on and off. Usually the typical and maximum gate charges  $(Q_g)$  are provided by manufacturers for switching the device under specified conditions. Because  $Q_g = C_g V_{\text{DD}}$ , the power loss in the driver can be calculated from (4) too:

$$P_{G} = C_{g}V_{DD}^{2}f_{SW} = Q_{g}V_{DD}f_{SW}$$

(4)

For example, for driving a power MOSFET with 50nC of gate charge ( $Q_g$  = 50nC) at 500kHz with  $V_{DD}$  = 12V, the driver loss due to gate charge will be 0.3W. For this driver that includes two channels, the total loss related to gate charge is doubled when driving similar MOSFETs:

$$P_{G} = 2 \times 50 \text{nC} \times 12 \text{V} \times 0.5 \text{MHz} = 0.6 \text{W}$$

(5)

When an external series gate resistor,  $R_g$ , is used for MOSFET or IGBT, a portion the  $P_G$  loss will dissipate on  $R_g$  and not inside the driver. With a simplified analysis, the gate driving loss inside each channel can be calculated by (6):

$$P_{G} = 0.5 \times Q_{g} \times V_{DD} \times f_{SW} \times \left( \frac{R_{OFF}}{R_{OFF} + R_{g}} + \frac{R_{ON}}{R_{ON} + R_{g}} \right)$$

(6)

Where  $R_{\text{OFF}}$  =  $R_{\text{OL}}$  is the effective pull-down resistance from the channel output to the ground and  $R_{\text{ON}}$  is the

effective resistance of the internal pull-up structure to VDD (in the SGM48523/4A/5/6).

To find the total loss in the device, the quiescent current losses ( $P_Q = I_{DD,Q} \times V_{DD}$ ) should be added. Due to small quiescent current ( $I_{DD,Q} \le 0.6 \text{mA}$ ) of the device, this loss is small and can be ignored. With  $V_{DD} = 12 \text{V}$  the quiescent loss is  $P_Q = 0.6 \text{mA} \times 12 \text{V} = 7.2 \text{mW}$ .

The actual driver supply current can be calculated as:

$$I_{DD} \approx \frac{P_{G}}{V_{DD}} \tag{7}$$

With  $P_G = 0.6W$  and  $V_{DD} = 12V$  the device supply current will be  $I_{DD} = 50mA$ .

## **Power Supply Recommendation**

The supply voltage ranges (V<sub>DD</sub>) for SGM48523/4A/5/6 are between 4.5V and 18V. The absolute maximum stress that the device tolerates is 20V. Considering a 2V margin for transient spikes, the maximum range is set to 18V. The minimum limit is dictated by the UVLO protection. In UVLO condition, the outputs are logic low, ignoring the input states. UVLO has an almost 0.35V hysteresis and an operating driver will not shut down unless  $V_{DD}$  falls below  $V_{OFF} = 3.85V$  (TYP). Therefore, it is important to make sure that for the designed system, the supply ripple or voltage drops do not fall below UVLO lower threshold that triggers device shutdown. A 100nF low ESR ceramic capacitor with another surface-mount capacitor of few microfarads between VDD and GND are necessary to prevent V<sub>DD</sub> transient drops. Similarly, at start-up, the device starts operation when the VDD pin voltage exceeds the V<sub>ON</sub> threshold (4.2V, TYP).

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original (JANUARY 2022) to REV.A

Page

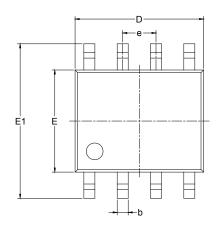

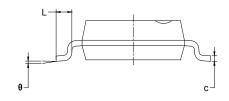

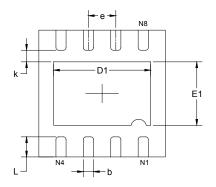

# PACKAGE OUTLINE DIMENSIONS SOIC-8

RECOMMENDED LAND PATTERN (Unit: mm)

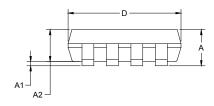

| Symbol |          | nsions<br>meters | Dimensions<br>In Inches |       |  |

|--------|----------|------------------|-------------------------|-------|--|

| ,      | MIN      | MAX              | MIN                     | MAX   |  |

| А      | 1.350    | 1.750            | 0.053                   | 0.069 |  |

| A1     | 0.100    | 0.250            | 0.004                   | 0.010 |  |

| A2     | 1.350    | 1.550            | 0.053                   | 0.061 |  |

| b      | 0.330    | 0.510            | 0.013                   | 0.020 |  |

| С      | 0.170    | 0.250            | 0.006                   | 0.010 |  |

| D      | 4.700    | 5.100            | 0.185                   | 0.200 |  |

| E      | 3.800    | 4.000            | 0.150                   | 0.157 |  |

| E1     | 5.800    | 6.200            | 0.228                   | 0.244 |  |

| е      | 1.27 BSC |                  | 0.050                   | BSC   |  |

| L      | 0.400    | 1.270            | 0.016                   | 0.050 |  |

| θ      | 0°       | 8°               | 0°                      | 8°    |  |

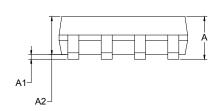

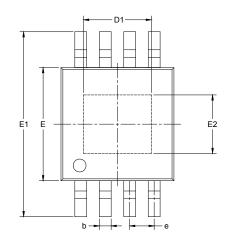

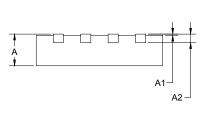

## PACKAGE OUTLINE DIMENSIONS

## MSOP-8 (Exposed Pad)

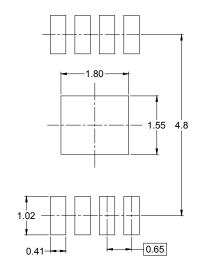

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol |       | nsions<br>meters | Dimensions<br>In Inches |       |  |

|--------|-------|------------------|-------------------------|-------|--|

|        | MIN   | MAX              | MIN                     | MAX   |  |

| Α      | 0.820 | 1.100            | 0.032                   | 0.043 |  |

| A1     | 0.020 | 0.150            | 0.001                   | 0.006 |  |

| A2     | 0.750 | 0.950            | 0.030                   | 0.037 |  |

| b      | 0.250 | 0.380            | 0.010                   | 0.015 |  |

| С      | 0.090 | 0.230            | 0.004                   | 0.009 |  |

| D      | 2.900 | 3.100            | 0.114                   | 0.122 |  |

| D1     | 1.700 | 1.900            | 0.067                   | 0.075 |  |

| е      | 0.65  | BSC              | 0.026                   | BSC   |  |

| E      | 2.900 | 3.100            | 0.114                   | 0.122 |  |

| E1     | 4.750 | 5.050            | 0.187                   | 0.199 |  |

| E2     | 1.450 | 1.650            | 0.057                   | 0.065 |  |

| L      | 0.400 | 0.800            | 0.016                   | 0.031 |  |

| θ      | 0°    | 6°               | 0°                      | 6°    |  |

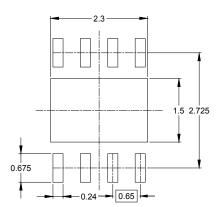

# PACKAGE OUTLINE DIMENSIONS TDFN-3×3-8L

**TOP VIEW**

**SIDE VIEW**

RECOMMENDED LAND PATTERN (Unit: mm)

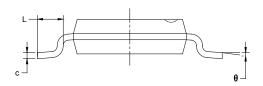

| Symbol | Dimensions<br>In Millimeters |       | Dimensions<br>In Inches |       |  |  |

|--------|------------------------------|-------|-------------------------|-------|--|--|

|        | MIN                          | MAX   | MIN                     | MAX   |  |  |

| Α      | 0.700                        | 0.800 | 0.028                   | 0.031 |  |  |

| A1     | 0.000                        | 0.050 | 0.000                   | 0.002 |  |  |

| A2     | 0.203 REF                    |       | 0.008 REF               |       |  |  |

| D      | 2.900                        | 3.100 | 0.114                   | 0.122 |  |  |

| D1     | 2.200                        | 2.400 | 0.087                   | 0.094 |  |  |

| E      | 2.900                        | 3.100 | 0.114                   | 0.122 |  |  |

| E1     | 1.400                        | 1.600 | 0.055                   | 0.063 |  |  |

| k      | 0.200 MIN                    |       | 0.008 MIN               |       |  |  |

| b      | 0.180                        | 0.300 | 0.007                   | 0.012 |  |  |

| е      | 0.650 TYP                    |       | 0.026 TYP               |       |  |  |

| L      | 0.375                        | 0.575 | 0.015                   | 0.023 |  |  |

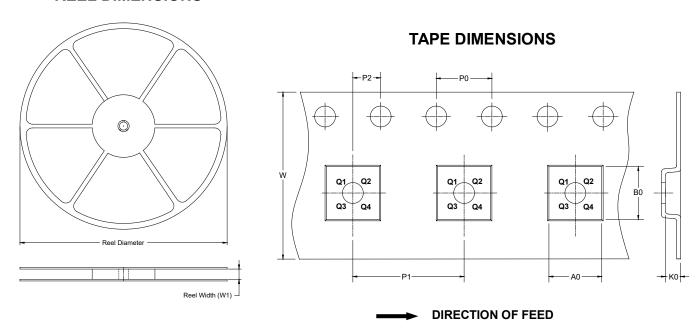

## TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type            | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOIC-8                  | 13"              | 12.4                     | 6.40       | 5.40       | 2.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| MSOP-8<br>(Exposed Pad) | 13"              | 12.4                     | 5.20       | 3.30       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| TDFN-3×3-8L             | 13"              | 12.4                     | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

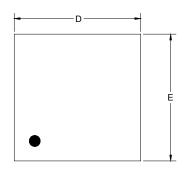

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-----------|----------------|---------------|----------------|--------------|

| 13"       | 386            | 280           | 370            | 5            |